# Table of Contents

| Article 1 Principle of Interface                               | 3       |

|----------------------------------------------------------------|---------|

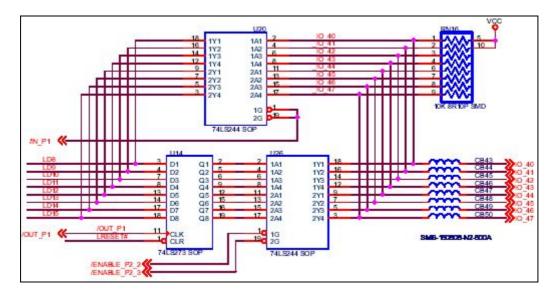

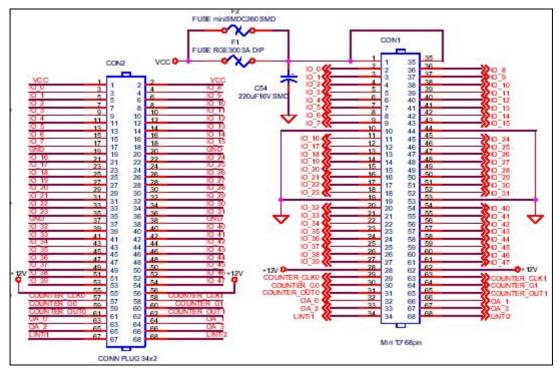

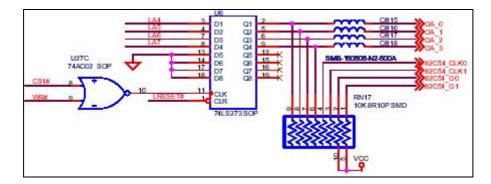

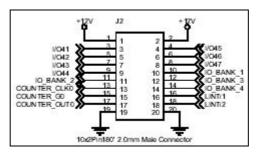

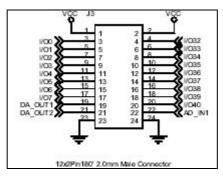

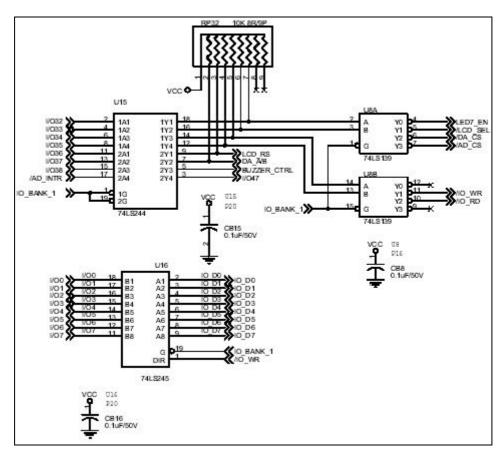

| Chapter 1 Brief Introduction of Computer and ISA Interface     | 4       |

| 1.1 PC XT/AT brief introduction                                | 4       |

| 1.2 PC XT/AT I/O address and memory configuration              | 5       |

| 1.3 Brief introduction of PC XT/AT interrupt concept           | 9       |

| 1.4 Brief introduction of chips like 8255/8254                 |         |

| 1.5 ISA interface brief introduction                           | 15      |

| 1.6 Summary of computer in recent years                        |         |

| 1.7 Recent computer structure                                  | 21      |

| 1.8 Brief introduction of related interface                    |         |

| 1.9 Operation rules applied to computer bits                   |         |

| Exercises:                                                     |         |

| Chapter 2 PCI interface                                        |         |

| 2.1 PCI (Peripheral Component Interconnect) brief introduction |         |

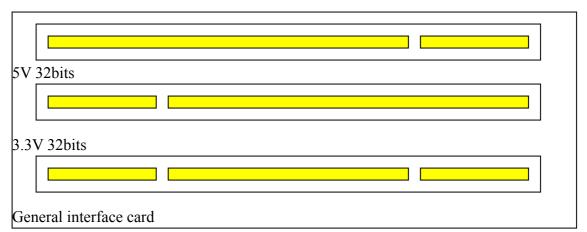

| 2.2 PCI connector and pin                                      |         |

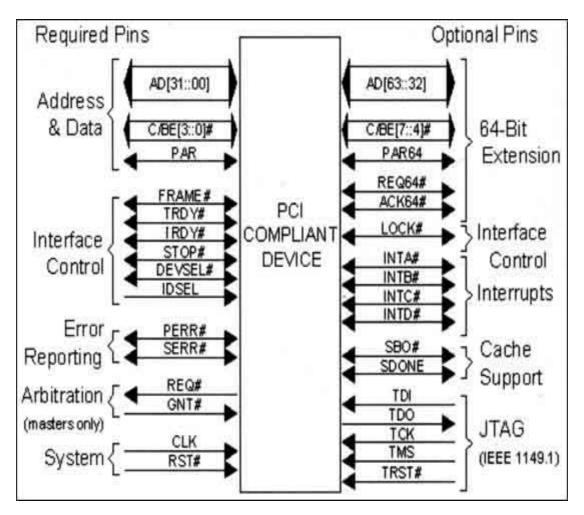

| 2.3 PCI interface pin definition                               |         |

| 2.4 PCI instructions                                           |         |

| 2.5 Configuration address port and configuration transaction   | 47      |

| 2.6 Configuration cache                                        | 54      |

| 2.7 Read transmission                                          | 60      |

| 2.8 Write transfer                                             | 65      |

| Exercises                                                      |         |

| Article 2 PCI-IO/LAB hardware description                      | 72      |

| Chapter 3 PCI-IO/LAB hardware                                  | 73      |

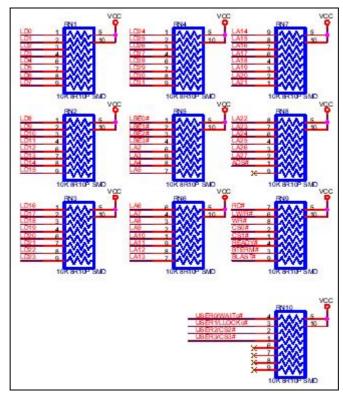

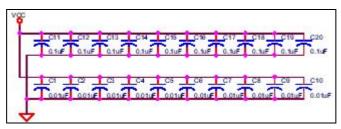

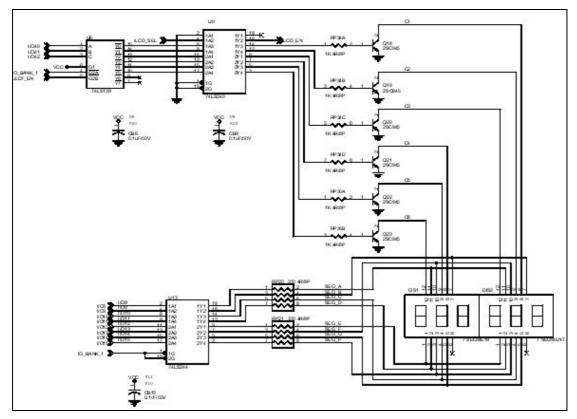

| 3.1 PCI-IO hardware                                            | 73      |

| 3.2 PCI-LAB hardware                                           |         |

| Chapter 4 Brief introduction of related chips                  | 91      |

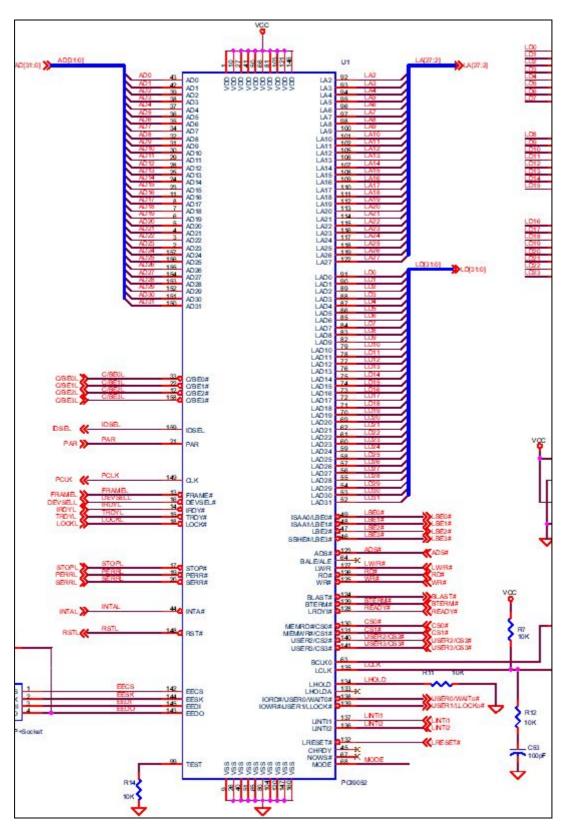

| 4.1 PLX9050/9052 chip                                          | 91      |

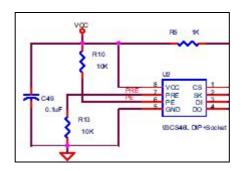

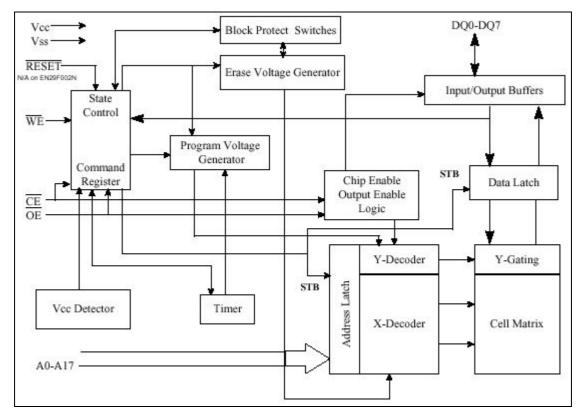

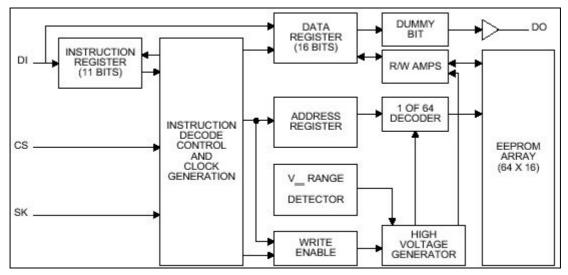

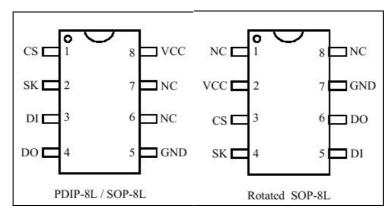

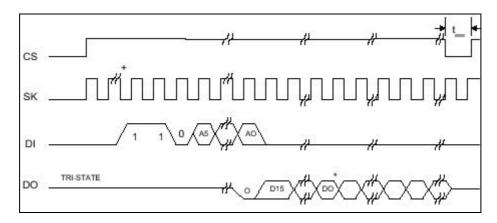

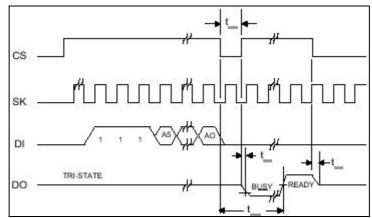

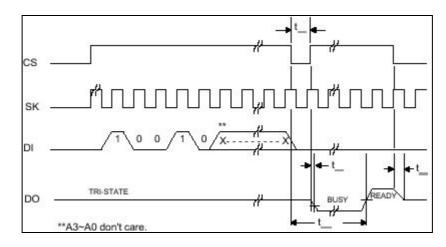

| 4.2 Serial RRPROM                                              | 96      |

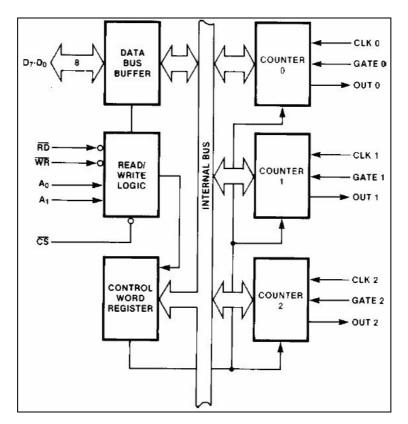

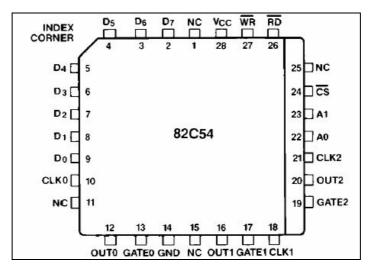

| 4.3 8254 timing/counting chip                                  |         |

| Article 3 PCI interface experiment software hardware basic     | setting |

| -                                                              |         |

| Chapter 5 PCI_LAB/IO software setting and description          |         |

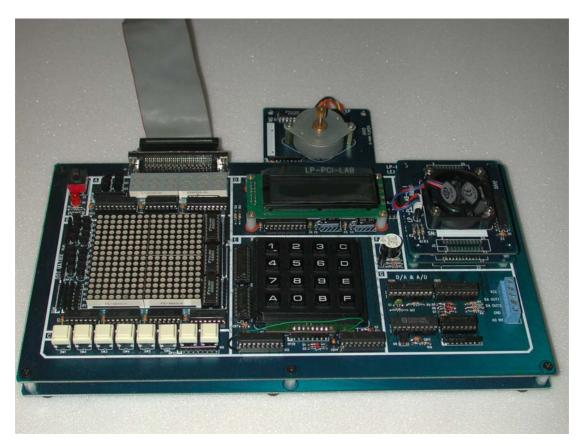

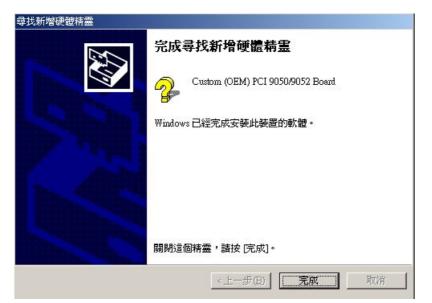

| 5.1 PCI experiment board hardware building                     | 115     |

| 5.2 PCI-IO drive program setting                               |         |

| 5.3 IO address of PCI-IO interface card                            | .123  |

|--------------------------------------------------------------------|-------|

| 5.4 Configuration cache                                            | .127  |

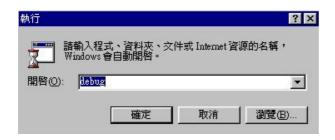

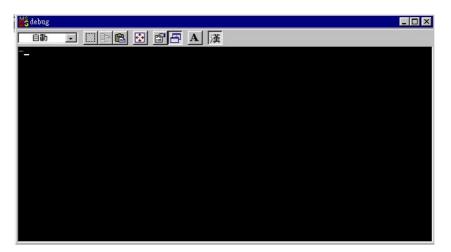

| 5.5 Use PCI-IO in Debug mode                                       | .129  |

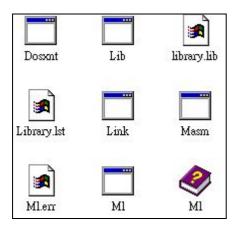

| 5.6 MASM assembly language setting                                 | .130  |

| 5.7 Visual C/C++ standard original setting                         | .131  |

| 5.8 Visual C/C++ 6.0 initial environment setting STEP by STEP      | .136  |

| Chapter 6 Program language description                             | .153  |

| 6.1 Debug mode instructions                                        | .153  |

| 6.2 MASM description                                               | .154  |

| 6.3 MASM instruction                                               | .155  |

| 6.4 PCI-IOin C/C++ program language instructions                   | .157  |

| 6.5 IO definition port of LEAP PCI-IO/LAB                          | .162  |

| 6.6 Visual C/C++ simple program compiling description              | .165  |

| Article 4 Basic PCI-LAB experiment examples                        | 167   |

| Chapter 7 Simple I/O experiment                                    | .168  |

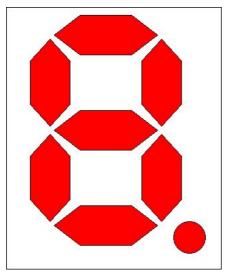

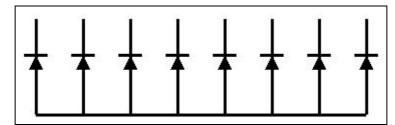

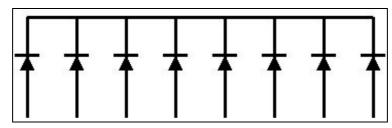

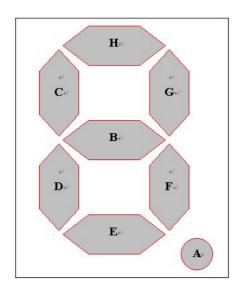

| 7.1 Seven-segment display experiment ( DEBUG Mode)                 | .170  |

| 7.2 Seven-segment display experiment (MASM)                        | .174  |

| 7.3 Seven-segment display experiment ( VC/C++)                     | .178  |

| 7.4 Drive multi-sets seven-segment LED display experiment ( MASM): | .180  |

| 7.5 Drive multi-sets seven-segment LED display experiment (VC/C++) | .185  |

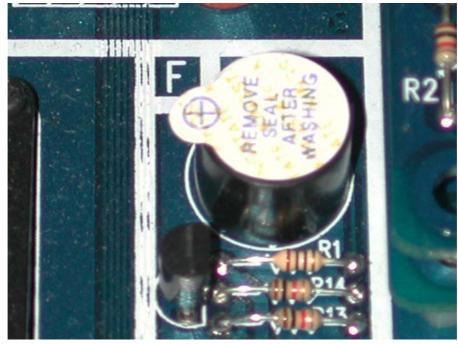

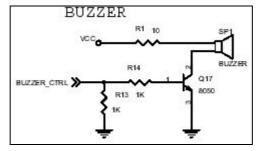

| 7-6 Buzzer experiment (Debug Mode & MASM)                          | .186  |

| 7.7 Buzzer experiment (VC/C++)                                     | .189  |

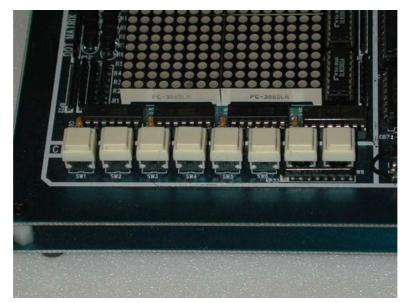

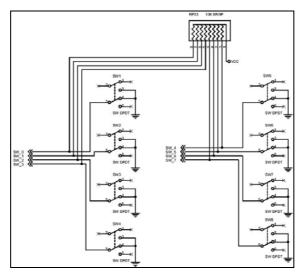

| 7.8 Pushbutton switches input experiment (Debug Mode & MASM)       | . 190 |

| 7.9 Pushbutton switch input experiment (VC/C++)                    | . 196 |

| Chapter 8 Motor and resistance heater                              | . 198 |

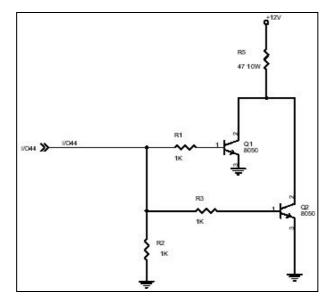

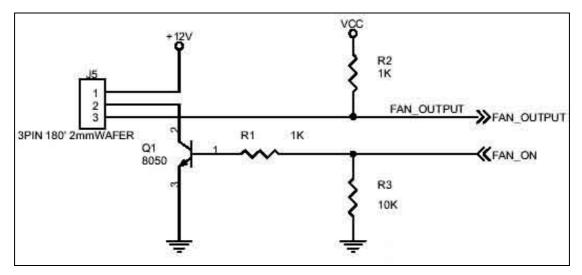

| 8.1 DC motor experiment (Debug Mode & MASM)                        | . 199 |

| 8.2 DC motor experiment (VC/C++)                                   | .202  |

| 8.3 Step motor experiment (Debug Mode)                             | .203  |

| 8.4 Step motor experiment (MASM)                                   | .205  |

| 8.5 Step motor experiment ( VC/C++)                                | .210  |

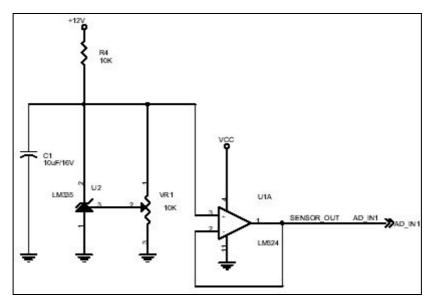

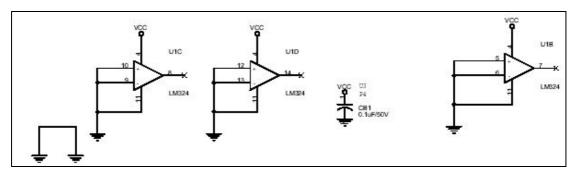

| 8.6 Resistance heater experiment                                   | .211  |

| 8.7 Temperature sensor and DC motor upstream signal                | .215  |

| Chapter 9 Dot matrix, keyboard and LCD                             | .217  |

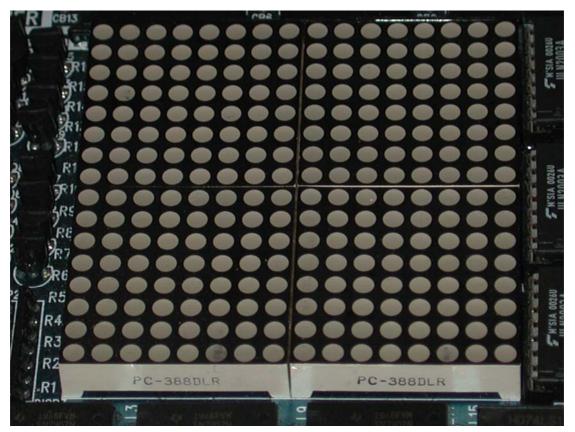

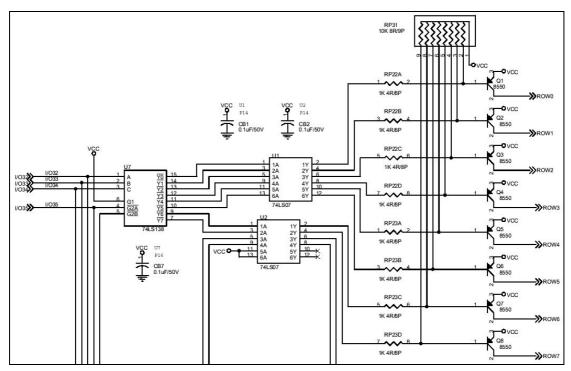

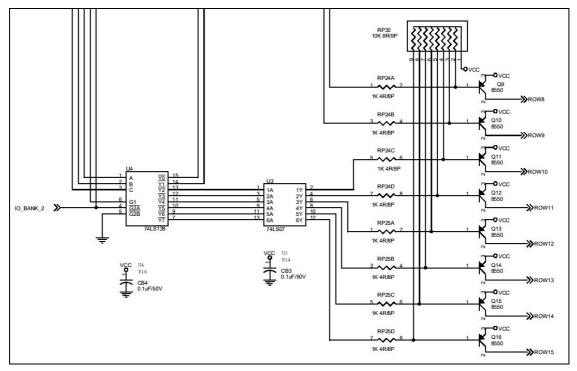

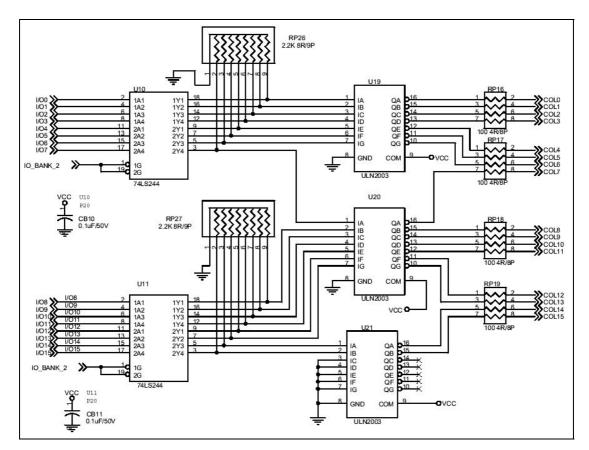

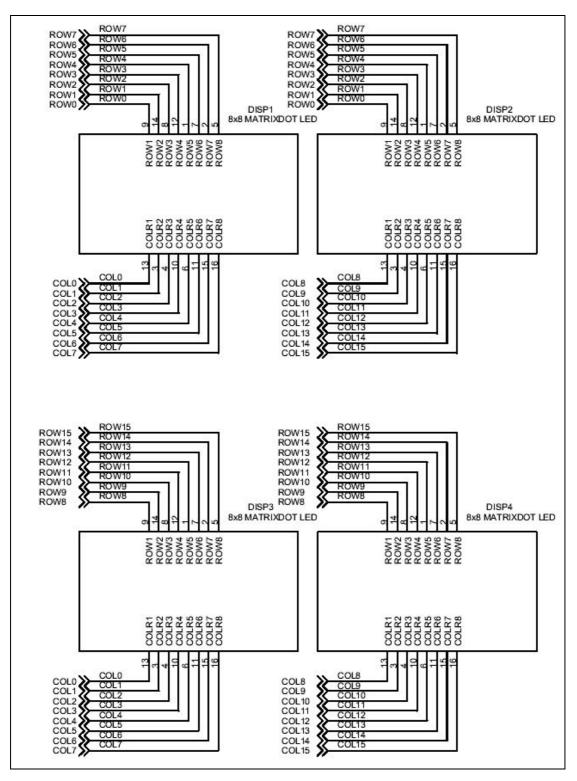

| 9.1 Dot matrix output experiment (Debug Mode & MASM)               | .217  |

| 9.2 Dot matrix output experiment (VC/C++)                          | .226  |

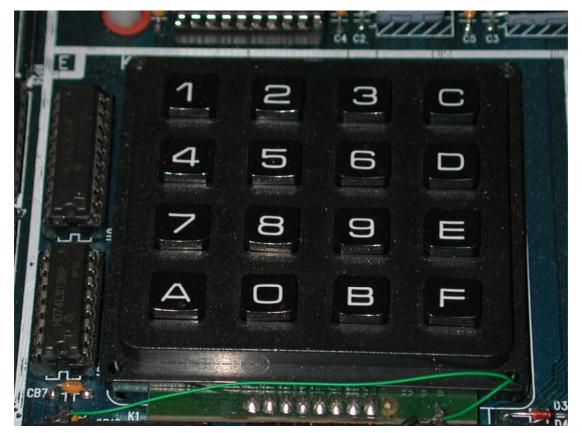

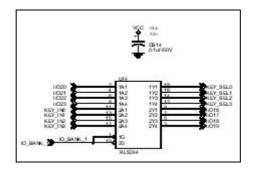

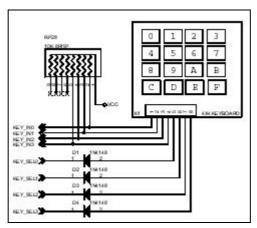

| 9.3 4 X 4 Keyboard input experiment (Debug Mode & MASM)            | .231  |

| 9.5 LCD                                                            | .243  |

| 9.6 LCD(MASM)                                                      | .251  |

|         | 9.7  | LCD (VC/C+     | +)              |           |       |       | 257     |

|---------|------|----------------|-----------------|-----------|-------|-------|---------|

|         | 9.8  | 8254 timer and | d counter       |           |       |       |         |

| Article | 5    | Advanced       | combined        | languages | and   | C/C++ | program |

| languag | ge s | amples         |                 | •••••     | ••••• |       |         |

| Cha     | pter | 10 Digital/ana | log converter   |           |       |       |         |

| Cha     | pter | 11 Analog/dig  | ital converter. |           |       |       |         |

| Cha     | pter | 12 Project and | IO-Port settin  | g program |       |       | 272     |

## **Article 1 Principle of Interface**

With the rapid development of computer technology, peripheral equipment and interface technology has also developed very quickly. The ISA interface of the so-called computer interface technology PC XT/AT, have not been manufactured since 2000. Computer motherboards with ISA interface are also no longer seen on the market, while PCI have already became a main interface for internal transmission of computer. Although computer host machine still have new types, the slow speed interface and AGP graphic interface, its main structure is unable to break away from PCI interface. In the future, speedier interface technologies will be developed based on this interface technology.

The so-called PCI interface has existed in computer system for more than ten years, however, people are still mostly familiar with the interface technology of ISA, which have been put into use for over 20 years and are appreciably different from PCI interface in bandwidth, frequency, related circuit design and research. This article will describe current computer structure and the principle of ISA interface, including a brief introduction of PC XT/AT and ISA, related I/O address configuration, interruption methods, introduction of ISA interface-related chips and their principles of operating. However, for in-depth discussion of the ISA interface, please refer to books associated with designs and applications of PC XT/AT and ISA interface first, and then proceed to discuss the PCI interface.

The chips mentioned in this book are all embodied in the chip specifications folder in the disk attached to this book, which can be used by the reader for references. This book mainly focuses on principles and practices of PCI interface, describes the basic principle of ISA interface in brief only for the reader to know the evolution of computer interface, thus to understand the related principle of PCI interface. Meanwhile, for practice and experiments of related ISA, please refer to interface books published in the market.

#### **Chapter 1 Brief Introduction of Computer and ISA Interface**

The development of ISA interface begins with PC XT/AT, so far, it has gone through decades of development and evolution. In the past, interface textbook practices were based on this. However, in recent years, due to the rapid development of semi-conductor and computer technology, the IAS interface is no longer the mainstream, and is gradually replaced by a more speedy computer interface. In spite of this, interface-related basic knowledge is still limited to ISA interface, far lagging behind current interface technology. This chapter describes the basic principle of the ISA interface, which can provide a basis and comparison for PCI interface and move ahead to build the conception of interface.

#### 1.1 PC XT/AT brief introduction

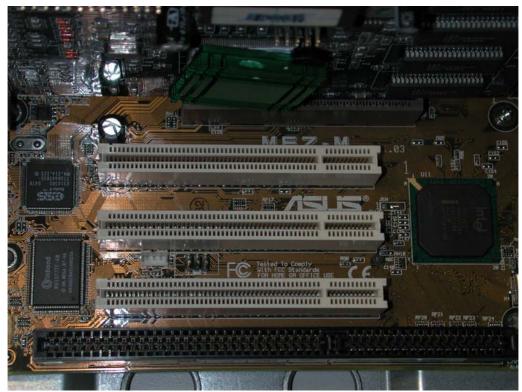

The personal computer or the so-called PC, which is the standard for personal computer established by IBM in the 1980s, belongs to an open system framework; and based on this standard, many manufacturers produced compatible personal computers, which greatly increased its popularity. Basic PC system uses INTEL X86 series CPU as operating core, initially it should work with X87 series floating-point unit to enhance its operating ability; after 80486 series, floating-point units are already included in the CPU, making its unnecessary to improve operating ability via selection. Several 8 bit extension slots are provided on PC XT motherboard for the use of related extension cards; however, in addition to several 8 bits extension slots on PC AT motherboard, another segment of the 8 bits extension slot is added, increasing the data bus to the standard of 16 bits. The above-mentioned extension slots are commonly known as ISA bus, after which, more compatible 32 bits buses have emerged, and finally, the PCI bus has became the mainstream.

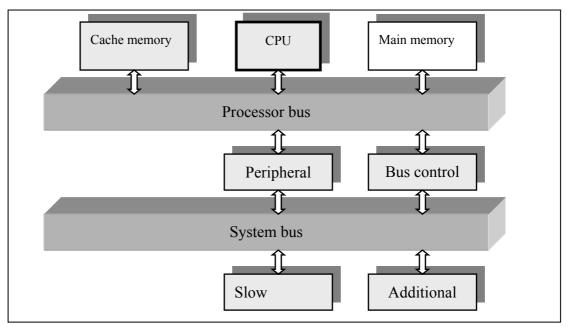

Figure 1-1-1 shows the basic PC system block diagram, in which internal exchange power supply provides electricity demands for the motherboard, on which are placed the microprocessor (CPU), memory (RAM/ROM), keyboard and speaker interface, counter, interruption controller and dynamic access memory (DMA) controller, via the extension slots, a few more interface cards, functions such display and serial communication can be added.

Figure 1-1-1 Basic PC system block diagram

#### 1.2 PC XT/AT I/O address and memory configuration

PC XT/AT data input and output are achieved by defining output and input ports. The address scope of CPU is 00000H~0FFFFH, between which there are 65536 output/input ports available for use. However, PC XT/AT system only uses 1024 ports between 0000H~03FFH. Moreover, these 1024 ports are divided into two parts, with A9/SA9 address line as the dividing line: when A9/SA9 is low, 512 ports between address 0000H~01FFH can be used, these ports are provided for the system motherboard to use; and when A9/SA9 is high, 512 ports between address 0200H~03FFH can be used, these ports are provided for related interface cards to use. Table 1-3-1 shows the I/O address configuration of PC XT/AT.

The maximum memory that can be addressed for PC XT is 1MB, while the maximum memory that can be addressed for PC AT is 16 MB, there is little difference between the two parts: 00000H~FFFFFH, the part that exceeds 1 MB is extended memory, which is the basis of today's computer memory. Table 1-2-2 shows the basic memory configuration diagram.

| Table | 1-2-1 | I/O | address | configuration |

|-------|-------|-----|---------|---------------|

|       |       |     |         |               |

| PC XT                      |                                            |

|----------------------------|--------------------------------------------|

| Address used (hexadecimal) | Description                                |

| 0000H~000FH                | 8237A DMA                                  |

| 0020H~0021H                | 8259A interrupt controller                 |

| 0040H~0043H                | 8253 timer                                 |

| 0060H~0063H                | 8255A peripheral interface controller      |

| 0080H~0083H                | DMA page controller                        |

| 00A0H~00BFH                | NMI mask bit                               |

| 00C0H~01FFH                | Reserved                                   |

| 0200H                      | Reserved                                   |

| 0201H                      | Pc game control interface card             |

| 0202H~0277H                | Reserved                                   |

| 0278H~027FH                | The second print port interface card       |

| 0280H~02F7H                | Reserved                                   |

| 02F8H~02FFH                | The second serial port interface card      |

| 0300H~031FH                | Reserved                                   |

| 0320H~033FH                | PC XT hard drive                           |

| 0338H~0377H                | Reserved                                   |

| 0378H~037FH                | Print port interface card                  |

| 0380H~03AFH                | Reserved                                   |

| 03B0H~03BFH                | Single color and print port interface card |

| 03C0H~03CFH                | Reserved                                   |

| 03D0H~03DFH                | Color graphics interface card              |

| 03E0H~03EFH                | Reserved                                   |

| 03F0H~03F7H                | 5 1/4 inch drive interface card            |

| 03F8H~03FFH                | Serial port interface card                 |

| PC AT                      |                                         |

|----------------------------|-----------------------------------------|

| Address used (hexadecimal) | Description                             |

| 0000H~001FH                | DMA controller 1 (8237A-5)              |

| 0020H~003FH                | Interrupt controller 1 (8259A,main)     |

| 0040H~005FH                | Timer 8254                              |

| 0060H~006FH                | 8042 keyboard controller                |

| 0070H~007FH                | Real-time clock and NMI mask register   |

| 0080H~009FH                | DMA page register (74LS612)             |

| 00A0H~00BFH                | Interrupt controller 2 (8259A)          |

| 00C0H~00DFH                | DMA controller 2 (8237A-5)              |

| 00F0H                      | Clear mathematics auxiliary processor   |

| 00F1H                      | Reset mathematics auxiliary processor   |

| 00F8H~00FFH                | Mathematics auxiliary processor         |

| 01F0H~01F8H                | Hard drive control card                 |

| 0200H~0207H                | Computer game control game              |

| 0278H~027FH                | Parallel printer control card2          |

| 02F8H~02FFH                | Serial transmission control card 2      |

| 0300H~031FH                | Prototyping card,                       |

| 0360H~036FH                | Reserved                                |

| 0378H~037FH                | Parallel printer control card 1         |

| 0380H~038FH                | SDLC, binary synchronous                |

|                            | communication 2                         |

| 03A0H~03AFH                | SDLC, binary synchronous                |

|                            | communication 1                         |

| 03B0H~03BFH                | Single color display interface card and |

|                            | printer control                         |

| 03C0H~03CFH                | Enhanced color drawing control care     |

| 03D0H~03DFH                | Color drawing control card              |

| 03E0H~03E7H                | Drive control card                      |

| 03F8H~03FFH                | Serial transmission control card 1      |

| PC XT         |                                  |                          |

|---------------|----------------------------------|--------------------------|

| Address       | Function                         | Description              |

| (hexadecimal) |                                  |                          |

| 0000~3FFF     | 128~256K system version, RAM     | System basic memory      |

| 40000~9FFFF   | Memory extension card plugged    | Intension memory         |

|               | into system intension slot       |                          |

| A0000~AFFFF   | Reserved                         | Use of interface cards   |

| B0000~B3FFF   | Single color image display       | compatible with PC / XT  |

| B4000~B7FFF   | Reserved                         |                          |

| B8000~BBFFF   | Color / graphic image displayed  |                          |

|               | (only 16K is used)               |                          |

| BC000~BFFFF   | Reserved                         |                          |

| C0000~C7FFF   | Reserved                         | Extension and control of |

| C8000~CBFFF   | Hard disk drive interface card   | 192K ROM                 |

| CC000~EFFFF   | Reserved                         |                          |

| F0000~F3FFF   | Reserved                         |                          |

| F4000~F5FFF   | Empty sockets left on the system |                          |

|               | board                            |                          |

| F6000~FDFFF   | BASIC interpreter                |                          |

| FE000~FFFFF   | BIOS                             |                          |

Table 1-2-2 Memory configurations

| PC AT           |                               |                                  |

|-----------------|-------------------------------|----------------------------------|

| Address         | Function                      | Description                      |

| (hexadecimal)   |                               |                                  |

| 000000H~07FFFFH | System board memory           | 512KB Memory on the              |

|                 |                               | motherboard is 512 KB in total   |

| 080000H~09FFFFH | Memory extension board        | Extend memory to 640K            |

| 0A0000H~0BFFFFH | Display buffer                | Buffer zone of character and     |

|                 |                               | painting                         |

| 0C0000H~0DFFFFH | Output/input read only        | Use of interface card            |

|                 | extension area                | output/input program             |

| 0E0000H~0EFFFFH | Read only memory area         | Reserved for the user to extend. |

|                 | reserved by the system        |                                  |

| 0F0000H~0FFFFFH | (BIOS) System basic           | System's start-up self-test,     |

|                 | input/output program area     | interrupt service program        |

|                 |                               | storage area (BIOS)              |

| 100000H~FDFFFH  | Maximum memory area           | Extending 15 MB memory           |

| FE0000H~FEFFFH  | System memory reserved area   | Reserved for the user to extend. |

| FF0000H~FFFFFFH | Basic I/O system program area | System's start-up self-test,     |

|                 |                               | interrupt service program        |

|                 |                               | storage area (BIOS)              |

#### 1.3 Brief introduction of PC XT/AT interrupt concept

PC XT/AT computer system I/O service can be divided into 3 types: POLLING, INTERRUPT and DMA; to carry out I/O service by means of POLLING, the overall system efficiency is the worst, because its system CPU needs to continuously check related peripherals, causing the system to waste a lot of time on I/O checks; to carry out I/O service by means of INTERRUPT, the system efficiency is high, interrupt request is sent by I/O device to the system, in comparison with the POLLING method, it can reduce the time for CPU needed to check related peripherals; and to carry out I/O service by means of DMA in order to make use of DMA. When interruption occurs, I/O device sends out DMA request, allowing I/O device to exchange data with system memory directly and the data need not be read and written by CPU, thus the overall transmission efficiency is the highest.

As for practice, interruption types can be divided into software interrupts and hardware interrupts. Also PC XT/AT can use 256 interrupts in total and use the method of interrupt vector to facilitate processing-interrupt vector from the computer is achieved by assigning a memory block, which is the so-called interrupt vector table;

the interrupt vector table is located in the memory absolute address scope 0000:0000H~0000:03FFH, each interrupt vector can allocate 4 memory addresses, so that the first address of each interrupt is interrupt vector multiplies 4. Software interrupt is to achieve the goal of interrupt by using INT instruction, still needs to refer to and use the contents of the interrupt vector table, which is quite convenient in practice. PC XT/AT hardware interrupts handle peripheral interrupt request signal with one or two 8259, while peripheral devices informs the system to interrupt by means of hardware implementation. Table 1-3-1 shows the functions of PC XT/AT hardware direct memory access; and table 1-3-3 lists bit configuration currently used for common X86 series platforms.

| Interrupt       | PC XT        |          | -    | PC AT            |                     |

|-----------------|--------------|----------|------|------------------|---------------------|

| signal          | Vector       | Function | •    | Vector value     | Function            |

| (interrupt      | value        |          |      |                  |                     |

| group)          |              |          |      |                  |                     |

| IRQ0 (1)        | 8            | System   |      | 8(08H)           | System counter      |

|                 |              | counter  |      |                  |                     |

| IRQ1 (1)        | 9            | Keyboard |      | 9(09H)           | Keyboard            |

| IRQ2 (1)        | 10           | Reserved | ,    | The second 8259  | -                   |

| IRQ3 (1)        | 11           | COM2     |      | 11(0BH)          | COM2                |

| IRQ4 (1)        | 12           | COM1     |      | 12(0CH)          | COM1                |

| IRQ5 (1)        | 13           | HDD      |      | 13(0DH)          | LPT2                |

| IRQ6 (1)        | 14           | FDD      |      | 14(0EH)          | FDD                 |

| IRQ7 (1)        | 15           | LPT      |      | 15(0FH)          | LPT1                |

| IRQ8 (2)        | Unused       |          |      | 70(46H)          | RTC                 |

| IRQ9 (2)        |              |          |      | 71(47H)          | Point to IRQ2       |

| IRQ10 (2)       |              |          |      | 72(48H)          | Reserved            |

| IRQ11 (2)       |              |          |      | 73(49H)          | Reserved            |

| IRQ12 (2)       |              |          |      | 74(4AH)          | Reserved            |

| IRQ13 (2)       | ]            |          |      | 75(4BH)          | Floating-point unit |

| IRQ14 (2)       | ]            |          |      | 76(4CH)          | HDD                 |

| IRQ15 (2)       |              |          |      | 77(4DH)          | Reserved            |

| Interrupt prior | ity sequence | ;        | 0>1> | >2(8>9>10>11>12> | 13>14>15)>3>4>5>6>7 |

Table 1-3-1 Function description of hardware interrupt request

| Channel number (DMA | Function                                       |

|---------------------|------------------------------------------------|

| controller groups)  |                                                |

| 0(1)                | DRAM update                                    |

| 1 (1)               | The secondary DMA controller                   |

| 2 (1)               | Use of floppy disk                             |

| 3 (1)               | Open to use                                    |

| 4 (2)               | Connected to the first group of DMA controller |

| 5 (2)               | Open to use                                    |

| 6 (2)               | Open to use                                    |

| 7 (2)               | Open to use                                    |

| Priority sequence   | 0>1 (4>5>6>7) >2>3                             |

Table 1-3-2 Hardware direct memory access function

| Name of I/O system or peripheral interface                       | I/O address  |

|------------------------------------------------------------------|--------------|

|                                                                  | (group)      |

| DMA Controller                                                   | 00h~0Fh (1)  |

|                                                                  | C0h~DFh (2)  |

| Programmable Interrupt Controller                                | 20h, 21h (1) |

|                                                                  | A0h, A1h (2) |

| Programmable counter (Programmable Interval Timer)               | 40h~43h (1)  |

|                                                                  | 44h~47h (2)  |

| Keyboard Controller                                              | 60h~64h      |

| Programmable Option Controller                                   | 90h~96h      |

| Floating-point auxiliary operation processor (Math Co-Processor, | F0h~FFh      |

| X87)                                                             |              |

| Secondary IDE interface                                          | 170h~177h    |

| Primary IDE interface card                                       | 1F0h~1F7h    |

| GAME I/O joystick interface (Game Port)                          | 200h~201h    |

| Sound Card interface                                             | 220h~22Fh    |

| PnP Configuration Register                                       | 279h, A79h   |

| (Serial Port 4 interface                                         | 2E8h~2EFh    |

| Serial Port 2 interface                                          | 2F8h~2FFh    |

| MIDI interface (Midi Port)                                       | 330h, 331h   |

| Parallel Port interface                                          | 378h~37Ah    |

| Single color graphic display interface (MDA/MGA)                 | 3B0h~3BFh    |

| Color graphic display interface (EGA/VGA)                        | 3C0h~3CFh    |

| Display cache (CGA/CRT)                                          | 3D4h~3D9h    |

| Serial Port 3 interface                                          | 3E8h~3EFh    |

| Floppy Diskette interface                                        | 3F0h~3F7h    |

| Enhanced IDE interface                                           | 3F6h, 3F7h   |

| Serial Port 1 interface                                          | 3F8h~3FFh    |

| PCIconfiguration address cache (PCI Configuration                | 0CF8h        |

| Register/Address)                                                |              |

| PCIconfiguration data read/write port (PCI Configuration         | 0CFCh        |

| Register/Data)                                                   |              |

Table 1-3-3 Current I/O address configuration

#### 1.4 Brief introduction of chips like 8255/8254

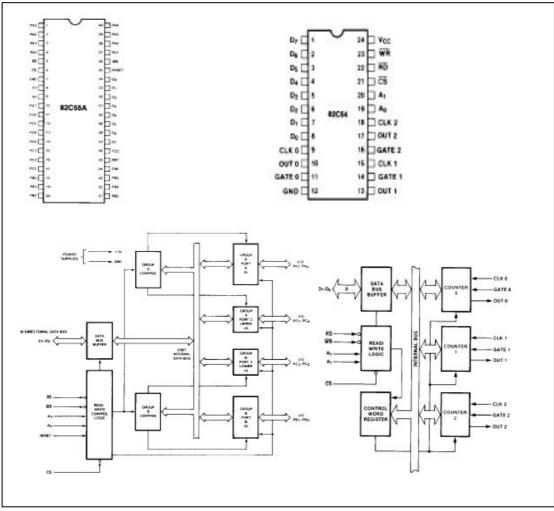

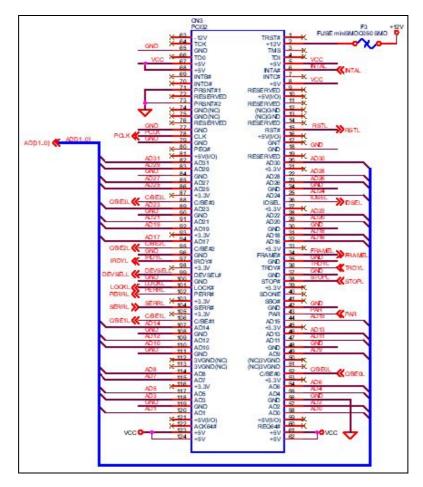

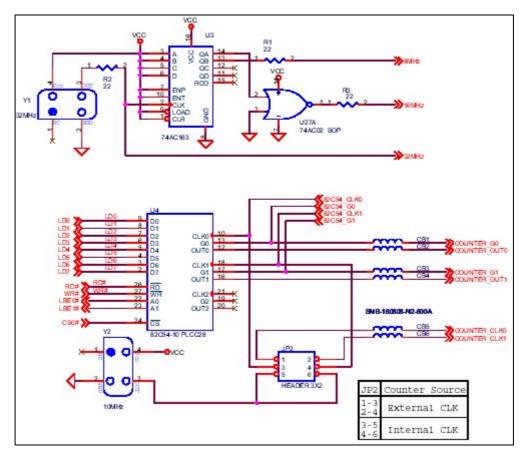

For PC XT/AT conventional ISA interfaces, chips like 8255 and 8254 play very important roles. 8255 is a 40 pin programmable peripheral interface chip, which can achieve very control functions through program language software planning; this chip has 24 I/O bits, and is generally divided into three 8 bits I/O ports: A, B, C, or divided into two 12 bits I/O groups: A, B, whereby group A is made up of A port and upper half 4 bits on C port, while group B is made up of B port and lower half 4 bits on port C. The I/O mode of this chip can be divided into 3 types: mode 0, mode 1 and mode 2, port A can operate the above 3 modes, port B can only operate mode 0 and mode 1, and operating mode is determined by controlling the control field of register. 8254 is a 24 pin programmable timer/counter chip, can be used to solve timing control problems, inside which there are 3 independent 16 bit counting-backward counters, which can handle binary and decimal counting, yet its operating mode can be planned into 6 modes such as mode 0 to 5; chip planning action is carried out by controlling the control field of the cache. Figure 1-4-1 shows the external pin diagram and internal structure diagram of 8255 and 8254.

Other ISA interface related chips include 8259 of interrupt control chip, keyboard and display interface chip 8279 and communication element 8251,etc. 8259 is a 28 pin programmable interrupt controller, which can handle the priority Sequence of 8 groups of 8 interrupt requests; PC XT uses a 8259 chip, while PC AT connects two 8259 chips in series, which is connected to the auxiliary 8259 interrupt controller via main 8259 interrupt controller IRQ2, solving the problem of interrupt controller compatibility and extension; request input can be interrupted by connecting several groups of 8259 extension in series. For the uses of ISA interface-related chips, they can be further discussed in books about PC XT/AT.

As with ISA interface operation, when used under peripheral chips like 8255, 8259, etc. It is necessary to set the action mode of peripheral chips, plan the operating modes of chips by defining control characters so as to write the relevant control programs. Table 1-4-1 shows the I/O addresses of relevant chips.

Figure 1-4-1 8255, 8254 pin and internal structure diagrams

| Chip | Function | Address | Description                    |

|------|----------|---------|--------------------------------|

| 8255 | PPI_PA   | 0x300   | 8255 A port address            |

|      | PPI_PB   | 0x301   | 8255 B port address            |

|      | PPI_PC   | 0x302   | 8255 C port address            |

|      | PPI_CW   | 0x303   | 8255 control character address |

| 8279 | D79      | 0x310   | 8279 data address              |

|      | C79      | 0x311   | 8279 control address           |

| 8254 | C0_54    | 0x320   | 8254 counter 0 address         |

|      | C1_54    | 0x321   | 8254 counter 1 address         |

|      | C2_54    | 0x322   | 8254 counter 2 address         |

|      | C3_54    | 0x323   | 8254 control address           |

| 8251 | D51      | 0x330   | 8251 data address              |

|      | C51      | 0x331   | 8251 control address           |

Table 1-4-1 ISA interface-related chip I/O address

## 1.5 ISA interface brief introduction

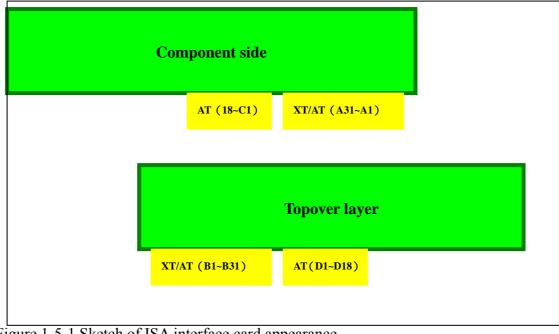

Table 1-5-1 is the ISA interface pin diagram, including the definition of another 8 bits extension pins. The signal pins are described by dividing into 4 types: table 1-5-2 describes data bus, table 1-5-3 describes address bus, and table 1-5-4 describes control bus, while the remaining power portion is described in 1-5-5. Figure 1-5-1 is the sketch of ISA interface card, describing the definition of interface card A/B sides.

Figure 1-5-1 Sketch of ISA interface card appearance

| TT 1 1 7    | 1 10 1 1 0      | •     |

|-------------|-----------------|-------|

| Inhia I 5   | 1 ISA interface | ning  |

| 1 auto 1-3- | I ISA Internace | DIIIS |

|             |                 | F     |

| PC  | AT       | PC  | XT     | Pin        | Slot | Pin | PC XT     |     | PC AT     |     |

|-----|----------|-----|--------|------------|------|-----|-----------|-----|-----------|-----|

| I/O | Signal   | I/O | Signal |            | 5101 | PIN | Signal    | I/O | Signal    | I/O |

| G   | GND      | G   | GND    | B1         |      | A1  | -I/OCHCK  | Ι   | -I/OCHCK  | Ι   |

| 0   | RESET    | 0   | RESET  | B2         |      | A2  | D7        | I/O | SD7       | I/O |

| Р   | +5       | Р   | +5     | B3         |      | A3  | D6        | I/O | SD6       | I/O |

| Ι   | IRQ9     | Ι   | IRQ2   | B4         |      | A4  | D5        | I/O | SD5       | I/O |

| Р   | -5       | Р   | -5     | B5         |      | A5  | D4        | I/O | SD4       | I/O |

| Ι   | DRQ2     | Ι   | DRQ2   | B6         |      | A6  | D3        | I/O | SD3       | I/O |

| Р   | -12      | Р   | -12    | B7         |      | A7  | D2        | I/O | SD2       | I/O |

| Ι   | OWS      | Ι   | NON    | <b>B</b> 8 |      | A8  | D1        | I/O | SD1       | I/O |

| Р   | +12      | Р   | +12    | B9         |      | A9  | D0        | I/O | SD0       | I/O |

| G   | GND      | G   | GND    | B10        |      | A10 | -I/OCHRDY | Ι   | -I/OCHRDY | Ι   |

| 0   | -SMEMW   | 0   | -MEMW  | B11        |      | A11 | AEN       | 0   | AEN       | 0   |

| 0   | -SMEMR   | 0   | -MEMR  | B12        |      | A12 | A19       | I/O | SA19      | I/O |

| I/O | -IOW     | I/O | -IOW   | B13        |      | A13 | A18       | I/O | SA18      | I/O |

| I/O | -IOR     | I/O | -IOR   | B14        |      | A14 | A17       | I/O | SA17      | I/O |

| 0   | -DACK3   | 0   | -DACK3 | B15        |      | A15 | A16       | I/O | SA16      | I/O |

| Ι   | DRQ3     | Ι   | DRQ3   | B16        |      | A16 | A15       | I/O | SA15      | I/O |

| 0   | -DACK1   | 0   | -DACK1 | B17        |      | A17 | A14       | I/O | SA14      | I/O |

| Ι   | DRQ1     | Ι   | DRQ1   | B18        |      | A18 | A13       | I/O | SA13      | I/O |

| I/O | -REFRESH | I/O | -DACK0 | B19        |      | A19 | A12       | I/O | SA12      | I/O |

| 0   | CLK      | 0   | CLK    | B20        |      | A20 | A11       | I/O | SA11      | I/O |

| Ι   | IRQ7     | Ι   | IRQ7   | B21        |      | A21 | A10       | I/O | SA10      | I/O |

| Ι   | IRQ6     | Ι   | IRQ6   | B22        |      | A22 | A9        | I/O | SA9       | I/O |

| Ι   | IRQ5     | Ι   | IRQ5   | B23        |      | A23 | A8        | I/O | SA8       | I/O |

| Ι   | IRQ4     | Ι   | IRQ4   | B24        |      | A24 | A7        | I/O | SA7       | I/O |

| Ι   | IRQ3     | Ι   | IRQ3   | B25        |      | A25 | A6        | I/O | SA6       | I/O |

| 0   | -DACK2   | 0   | -DACK2 | B26        |      | A26 | A5        | I/O | SA5       | I/O |

| 0   | T/C      | 0   | T/C    | B27        |      | A27 | A4        | I/O | SA4       | I/O |

| 0   | ALE      | 0   | ALE    | B28        |      | A28 | A3        | I/O | SA3       | I/O |

| Р   | +5       | Р   | +5     | B29        |      | A29 | A2        | I/O | SA2       | I/O |

| 0   | OSC      | 0   | OSC    | B30        |      | A30 | A1        | I/O | SA1       | I/O |

| G   | GND      | G   | GND    | B31        |      | A31 | A0        | I/O | SA0       | I/O |

| PC A  | T (ONLY) | — Pins    | Slots | Ding     | PC AT (ONLY) |     |

|-------|----------|-----------|-------|----------|--------------|-----|

| I/O   | Signal   | PINS      | Slots | Pins     | Signal       | I/O |

| Ι     | -MEMCS16 | D1        |       | C1       | SBHE         | I/O |

| Ι     | -I/OCS16 | D2        |       | C2       | LA23         | I/O |

| Ι     | IRQ10    | D3        |       | C3       | LA22         | I/O |

| Ι     | IRQ11    | D4        |       | C4       | LA21         | I/O |

| Ι     | IRQ12    | D5        |       | C5       | LA20         | I/O |

| Ι     | IRQ15    | D6        |       | C6       | LA19         | I/O |

| Ι     | IRQ14    | D7        |       | C7       | LA18         | I/O |

| 0     | -DACK0   | D8        |       | C8       | LA17         | I/O |

| Ι     | DRQ0     | D9        |       | С9       | -MEMR        | I/O |

| 0     | -DACK5   | D10       |       | C10      | -MEMW        | I/O |

| Ι     | DRQ5     | D11       |       | C11      | SD8          | I/O |

| 0     | -DACK6   | D12       |       | C12      | SD9          | I/O |

| Ι     | DRQ6     | D13       |       | C13      | SD10         | I/O |

| 0     | -DACK7   | D14       |       | C14      | SD11         | I/O |

| Ι     | DRQ7     | D15       |       | C15      | SD12         | I/O |

| Р     | +5       | D16       | ]     | C16      | SD13         | I/O |

| Ι     | -MASTER  | D17       | ]     | C17      | SD14         | I/O |

| G     | GND      | D18       | ]     | C18      | SD15         | I/O |

| P: po | wer      | G: ground | ]     | I: input | O:output     |     |

## Table 1-5-2 data bus

| Pin signal | Pin signal description | Transmission   |

|------------|------------------------|----------------|

|            |                        | direction      |

| SD0~sD7    | Low byte               | Bi-directional |

|            |                        | transmission   |

| SD8~sD15   | High byte              | Bi-directional |

|            |                        | transmission   |

## Table1-5-3 address bus

| Pin signal       | Pin signal description            | Transmission   |

|------------------|-----------------------------------|----------------|

|                  |                                   | direction      |

| $sA0 \sim sA19$  | PC XT base address bus            | Bi-directional |

|                  |                                   | Transmission   |

| $LA17 \sim LA23$ | PC At high byte addressing signal | Bi-directional |

|                  |                                   | Transmission   |

Table 1-5-4 control buses

| Signal group                  | Pin signal         | Pin signal description           | Transmission          |

|-------------------------------|--------------------|----------------------------------|-----------------------|

|                               |                    |                                  | direction             |

| System control                | RESET              | System reset, power on, system   | Output                |

| signals                       |                    | starts                           |                       |

|                               | ALE                | Address signal locking           | Output                |

|                               | AEN                | DMA and CPU cycle mode           | Output                |

|                               | <b>SMEMR</b>       | Memory read                      | Output                |

|                               | MEMR               |                                  | <b>Bi-directional</b> |

|                               | <b>SMEMW</b>       | Memory write                     | Output                |

|                               | MEMW               |                                  | <b>Bi-directional</b> |

|                               | ĪOR                | I/O read                         | Bi-directional        |

|                               | ĪOW                | I/O write                        | Bi-directional        |

|                               | MEM CS 16          | (O/C, T/S) memory data           | Input                 |

|                               | MEM CS 16          | transmission instruction         |                       |

|                               | <i>I / O CS</i> 16 | I/O data transmission            | Input                 |

|                               | <i>sBHE</i>        | High byte transmission start-up  | <b>Bi-directional</b> |

|                               | REFRESH            | DRAM regeneration instruction    | <b>Bi-directional</b> |

| Clock control                 | OSC                | Extension slot clock             | Output                |

| signal                        | CLK                | OSC/3, 1/3 system clock          | Output                |

| Asynchronous                  | I / OCH RDY        | Make CPU access slow             | Input                 |

| control signal                | <u>OWS</u>         | Place system access memory into  | Input                 |

|                               |                    | waiting status                   |                       |

| Interrupt request             | IRQ                | Hardware interrupt signal        | Input                 |

| signal                        | I/OCHCK            | Parity check error detecting     | Input                 |

| DMAcontrol                    | DRQ                | Direct memory access signal      | Input                 |

| signal                        | DACK               | Response signal sent by DMA      | Output                |

|                               | T/C                | TERMINAL COUNT                   | Output                |

| Double processor coordination | MASTER             | Multi-processor bus coordination | Input                 |

| Voltage<br>value                   | +5V                | -5V                  | +12V               | -12V                 | GND |

|------------------------------------|--------------------|----------------------|--------------------|----------------------|-----|

| Output<br>voltage<br>specification | 4.75V~5.25V<br>±5% | -4.75V~-5.25V<br>±5% | 11.4V~12.6v<br>±5% | -10.8V~13.2V<br>±10% |     |

| Output<br>current<br>specification | <15A               | <0.5A                | <5A                | <0.3A                |     |

Table 1-5-5 power signals

#### 1.6 Summary of computer in recent years

In recent years, computers have been breaking away from traditional structure by means of Legacy Free PCs. New generations of computers are designed with brand-new specifications; and in conjunction with newly defined hardware/software interface specifications, a new generation of personal computers have been manufactured. As seen from the motherboard platform layout, free of the constraints of traditional structures in the past and with ISA bus, ISA extension slots discarded, it supports only the latest, self-detecting/setting bus and interface specifications, such as PCI, AGP, USB, SM, Bus, etc; besides, sound card, modem interface cards are also gradually replaced by AMR or CNR interface.

Since Intel advocated USB, so far, most of the motherboards have a built-in USB interface, and USB devices are becoming popular gradually; currently the most popular motherboard is USB1.1 interface, even USB2.0 began to become popular so that traditional medium or low speed interface such as serial ports, parallel ports, joystick and PS/2 interface cards have been gradually abandoned. In addition to the USB interface, PCI interface, AGP display interface card or IEEE1394 interface are enough for common users to use. Table 1-6-1 describes the differences between "traditional" and "new generation" computers.

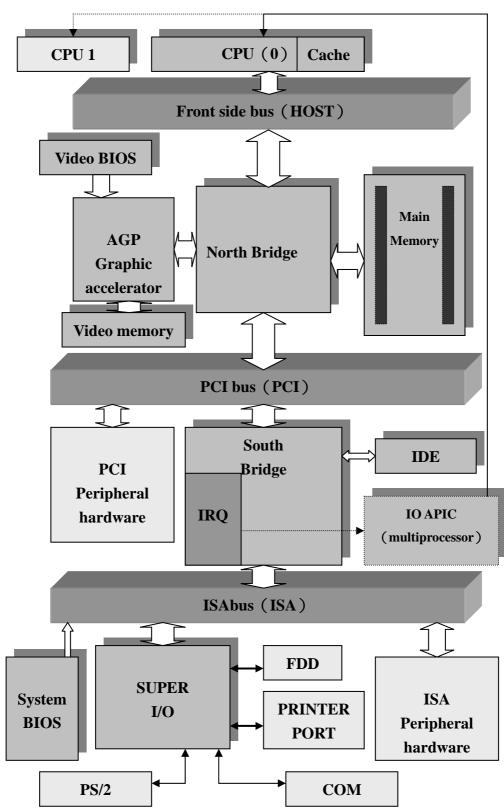

Figure 1-6-1 computer system structure diagrams

Nowadays, computer technology is developing very quickly and there are many chip manufacturers, so the chips are largely identical in terms of specifications and functions, however, there are still some differences in design details. Generally speaking, the structures of today's personal computers are described synoptically with X86 system. Figure 1-6-1 shows the X86 system structure with single/double CPUs. The difference between single and double CPUs lies in the structure of multi-mission hardware environment, so double CPUs need IO-APIC to manage interrupt. Host/PCI is commonly called the North Bridge, connects main processor bus and PCI bus. PCI-to-ISA Bridge is commonly called the South Bridge, connects PCI bus and ISA (or LPC) bus, usually integrating Interrupt Controller, IDE Controller, USB Host Controller, and DMA Controller, the South and North Bridges chipset. Today, many chipsets have replaced PCI interface to the South Bridge end.

|                                | Legacy PC (traditional | Legacy Free PC     |

|--------------------------------|------------------------|--------------------|

|                                | PC)                    |                    |

| Shape design                   | Fixed format, dull     | Diversified        |

| Main host dimension            | ATX, MicorATX          | MicorATX, FlexATX  |

| ISABus, ISASlot                | Yes (via LPC)          | None (fully        |

| PCI Bus                        | Yes                    | abandoned)         |

| AGP Bus                        | Yes (not a must)       | Yes                |

| USB Bus                        | Yes (a must)           | Yes (not a must)   |

|                                |                        | Yes (a must)       |

| Serial Port COM1 & COM2        | Yes                    | None (completely a |

| Infrared Port (IR)             | Yes (not a must)       | must)              |

| Parallel Port (LPT1)           | Yes                    | Yes (not a must)   |

| Game I/O                       | Yes                    | None (fully        |

|                                |                        | abandoned)         |

|                                |                        | None (fully        |

|                                |                        | abandoned)         |

| The function USB device can    | Yes (not a must)       | Yes (a must)       |

| directly start up the computer |                        |                    |

Table 1-6-1 the difference between traditional computer and new generation of computers

## 1.7 Recent computer structure

The configuration of memory and I/O address for recent computers was nearly completed in the era of 80386, except for some large main hosts, the configuration of memory is largely the same as that of PC AT, and the maximum memory limitation is

determined by the chipset. In theory, the maximum memory capacity that can be addressed on computers is 4GB, and basic I/O address is similar to the I/O address of PC AT.

Generally speaking, X86 system can use address line drives, access memory addresses or I/O port drive, there are only 16 I/O ports, so from 00000h~0FFFFh, I/O ports is 2<sup>16</sup>. In common ISA interface system, only 2<sup>10</sup>ports (0000h~03FFh) are used, while PCI interfacees use I/O ports over 0400h. PCI interface cards used in this practice are driven by I/O ports.

Also, X86 system designs 256 interrupt vectors from INT 01h to INT Fifth respectively, each vector contains 4 bytes; under real models, the memory address of interrupt vector tables are addressed between 0000: 0000 and 0000: 03FFh, using the 1KB memory space in the forefront. Table 1-7-1 shows the lists of interrupt vector numbers, which is related with the writing of assembly languages.

| Interrupt | Property   | The description of interruption meaning                     |  |  |

|-----------|------------|-------------------------------------------------------------|--|--|

| number    |            |                                                             |  |  |

| INT 00h   | (Error)    | CPU Divide Error                                            |  |  |

| INT 01h   | (Hardware) | CPU Single Step                                             |  |  |

| INT 02h   | (Hardware) | NMI (Non Mask able Interrupt)                               |  |  |

| INT 03h   | (Hardware) | Break Point code (instruction break point, instruction code |  |  |

|           |            | 0CCh)                                                       |  |  |

| INT 04h   | (Error)    | CPU Overflow (Data overflow break)                          |  |  |

| INT 05h   | (Software) | BIOS process, press Print screen button's print service     |  |  |

|           | (Error)    | program interface                                           |  |  |

|           |            | BOUND Range Exceed                                          |  |  |

| INT 06h   | (Error)    | Invalid Op Code                                             |  |  |

| INT 07h   | (Error)    | Floating Point Processor/FPU Not Available                  |  |  |

| INT 08h   | (Hardware) | IRQ0-System Timer (system timer interrupt)                  |  |  |

|           |            | INT 8 is generated every 1/18.2 second, used to carry out   |  |  |

|           |            | the work of system timing                                   |  |  |

| INT 09h   | (Hardware) | IRQ1-Keyboard Interrupt                                     |  |  |

|           | (Error)    | Processor Extension Protection ERROR (block selection       |  |  |

|           |            | extension directional error)                                |  |  |

| INT 0Ah   | (Hardware) | IRQ2-Connected to the auxiliary program of IRQ8~15          |  |  |

|           | (Error)    | Invalid Task State Segment (TSS), Invalid Task State        |  |  |

|           |            | Segment error                                               |  |  |

| INT 0Bh   | (Hardware) | IRQ3-COM2 (secondary serial port)                           |  |  |

|           | (Error)    | Segment not present (actual memory corresponding to the     |  |  |

|           |            | segment not present)                                        |  |  |

| INT 0Ch   | (Hardware) | IRQ4-COM1 (Primary serial port)                             |  |  |

|           | (Error)    | CPU Stack Fault, (CPU stack processing fault)               |  |  |

| INT 0Dh   | (Hardware) | IRQ5-LPT2 (secondary print port), now it is reserved for    |  |  |

|           | (Error)    | PnP system configuration                                    |  |  |

|           |            | GENERAL PROTECTION VIOLATION                                |  |  |

|           |            | CPU produces protection violation error                     |  |  |

| INT 0Eh   | (Hardware) | IRQ6-Floppy Diskette read/write interrupt                   |  |  |

|           | (Error)    | PAGEFAULT Switch page fault                                 |  |  |

| INT 0Fh   | (Hardware) | IRQ7-LPT1 primary print port                                |  |  |

| INT 10h   | (Software) | Screen I/O interface, switch character/graphics mode.       |  |  |

|           |            | Providing display/paint scroll service                      |  |  |

| INT 11h   | (Software) | PC peripheral equipment check                               |  |  |

|           |            |                                                             |  |  |

Table 1-7-1 Interrupt vectors numbers lists

| INT 11h | (Software) | Data/address alignment check error, occurring to CPU          |  |

|---------|------------|---------------------------------------------------------------|--|

|         |            | above 486                                                     |  |

| INT 12h | (Software) | Sending back PC main memory size check                        |  |

|         | (Error)    | MACHINE CHECK EXCEPTION                                       |  |

| INT 13h | (Software) | Disk I/O interface (services such as floppy diskette, hard    |  |

|         |            | disk read/write, format)                                      |  |

| INT 14h | (Software) | Serial Port Communication port interrupt service routine      |  |

| INT 15h | (Software) | Cassette interface service program, AT extension interrupt    |  |

|         |            | service call, numerous programs                               |  |

| INT 16h | (Software) | Keyboard read service program                                 |  |

| INT 17h | (Software) | Print service program                                         |  |

| INT 18h | (Software) | ROM BASIC entry point address, network card Diskette          |  |

|         |            | Start-up interception point                                   |  |

| INT 19h | (Software) | Entry point of starting up the operating system               |  |

| INT 1Ah | (Software) | BIOS time interface/CMOS Real-time Clock battery clock        |  |

|         |            | interface                                                     |  |

| INT 1Bh | (Software) | Interrupt entry point handling program of CTRL BREAK          |  |

|         |            | for BIOS                                                      |  |

| INT 1Ch | (Software) | User timing interrupt, process auxiliary program call from    |  |

|         |            | INT 8                                                         |  |

| INT 1Dh | (Hardware) | Video interface card address table                            |  |

| INT 1Eh |            | Floppy diskette parameter address table                       |  |

| INT 1Fh |            | Character dot matrix fonts table address (ASC80h $\sim$ 0FFh) |  |

| INT 20h |            | MS-DOS end program execution                                  |  |

| INT 21h | (Software) | MS-DOS API                                                    |  |

| INT 22h | (Software) | MS-DOS program ends jump address                              |  |

| INT 23h | (Software) | MS-DOS program presses the interrupt entry point of           |  |

|         |            | CTRL BREAK                                                    |  |

| INT 24h | (Software) | MS-DOS Fatal Error Handler                                    |  |

| INT 25h | (Software) | DOS Absolute Read                                             |  |

| INT 26h | (Software) | DOS Absolute Write                                            |  |

| INT 27h | (Software) | Permanent memory interface in. COM file                       |  |

| INT 28h | (Software) | System call of DOS idle state                                 |  |

| INT 29h | (Software) | DOS Console Output                                            |  |

| INT 2Ah |            | Network software interface layer, Net BIOS                    |  |

| INT     | (Software) | Reserved and unused                                           |  |

| 2Bh~2Dh |            |                                                               |  |

| INT 2Eh                                                                       | (Software) | Transmit command queue parameters to DOS command                                           |  |  |

|-------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------|--|--|

| NIT OF                                                                        | (C - A)    | interpreter                                                                                |  |  |

| INT 2Fh                                                                       | (Sonware)  | Multiplex Interrupt Multiplex system Interrupt CD-ROM, HIMEM.SYS (XMS), Windows&DPMI Check |  |  |

| INT 30h                                                                       | (Software) | Reserved and unused                                                                        |  |  |

| INT 31h                                                                       | (Software) | DOS protection mode                                                                        |  |  |

| INT 32h                                                                       | (Software) | Reserved and unused                                                                        |  |  |

| INT 33h                                                                       | (Software) | Mouse interrupt service                                                                    |  |  |

| INT 34h~3Eh                                                                   | (Software) | Used for floating-point unit                                                               |  |  |

| INT 3Fh                                                                       | (Software) | Overlay Manager                                                                            |  |  |

| INT 40h                                                                       | (Software) | Disk interrupt service program                                                             |  |  |

| INT 41h                                                                       |            | Primary hard disk parameter address table                                                  |  |  |

| INT 42h                                                                       | (Software) | INT 10h display service                                                                    |  |  |

| INT 43h                                                                       |            | Dot matrix fonts data table address                                                        |  |  |

| INT 44h                                                                       |            | Dot matrix fonts data table address                                                        |  |  |

| INT 45h                                                                       | (Software) | Reserved and unused                                                                        |  |  |

| INT 46h                                                                       |            | Secondary hard disk parameter address table                                                |  |  |

| INT 47h~49h                                                                   | (Software) | Reserved and unused                                                                        |  |  |

| INT 4Ah                                                                       | (Software) | CMOS/RTC Alarm Interrupt                                                                   |  |  |

| INT 4Bh~64h                                                                   | (Software) | Reserved and unused                                                                        |  |  |

| INT 65h                                                                       | (Software) | Audio call service program                                                                 |  |  |

| INT 66h                                                                       | (Software) | Reserved and unused                                                                        |  |  |

| INT 67h                                                                       | (Software) | LIMEMS service                                                                             |  |  |

| INT 68h~6Fh                                                                   | (Software) | Reserved and unused                                                                        |  |  |

| INT 70h                                                                       | (Hardware) | IRQ8 CMOS/RTC Time Interrupt                                                               |  |  |

| INT 71h                                                                       | Hardware   | IRQ9 (pointing to IRQ2-INT 0Ah)                                                            |  |  |

| INT 72h                                                                       | Hardware   | IRQ10 (PnP)                                                                                |  |  |

| INT 73h                                                                       | Hardware   | IRQ11 (PnP)                                                                                |  |  |

| INT 74h                                                                       | Hardware   | IRQ12 (PS/2, USB)                                                                          |  |  |

| INT 75h                                                                       | Hardware   | IRQ13 (Co-Processor – X87)                                                                 |  |  |

| INT 76h                                                                       | Hardware   | IRQ14 (Primary IDE)                                                                        |  |  |

| INT 77h                                                                       | Hardware   | IRQ15 (Secondary IDE)                                                                      |  |  |

| INT 78h~7Fh                                                                   | (Software) | Reserved and unused                                                                        |  |  |

| INT 80h~Efh                                                                   | (Software) | BASIC interpretation program                                                               |  |  |

| INT F0h~FFh                                                                   | (Software) | Reserved and unused                                                                        |  |  |

| (Software): services of software call; (hardware): IRQ hardware interruption; |            |                                                                                            |  |  |

| (error): error d                                                              | letection  |                                                                                            |  |  |

#### 1.8 Brief introduction of related interface

Nowadays, computer systems are developing very quickly and specifications of CPU, memory, peripheral hardware and motherboard chipset are likewise expanding rapidly and varied. However, transmission specifications and interfaces are not easy to change. Interfaces commonly seen on common personal computers include the SM Bus, USB, IEEE1394, IDE, AGP and PCI, etc, while AC97, LPC and SCSI are rarely seen. In the following paragraphs, we will briefly describe interfaces such as AC97, SM Bus, USB, LPC, while AGP, SCSI, IEEE1394 will not be described.

#### AC'97 (Audio Codec 97)

AC97 is Analog Component 97 (for short AC97), which was introduced by Intel96 when developing NSP MULTI-MEDIA; its latest version is V2.1 (issued on May 22nd, 1998), and became the later CNR 1.0 specification through subsequent extension. AC 97 mainly include analog/digital conversion circuit functions such as computer platforms (motherboard), sound card chip, modem transmission chips, which are divided into Analog Codec and Digital Codec; pure Digital Codec is placed on motherboard, while Analog Codec is located on Riser Card of extension slot. Signals are controlled and transmitted by motherboards (chipsets) with AC-Link, which can reduce the interference from high frequency signals of the motherboard and improve the sound quality of built-in audio chip motherboard. This extension slot is called the AMR slot.

Another characteristic of AC97 is that it can enable low pin and low cost Analog Codec designed in compliance with AC97 specifications, through the increasingly powerful operating abilities of CPU, to simulate 16 bit sound blaster level recording, playing sound and MIDI sound play function. Modem Codec in conformity with AC 97 simulates the basic 56Kbps modem function of V90 specification by means of software, or the two can be integrated into AMC (Audio/Modem Codec) of audio/modem transmission. As with the mixer, it can be outputted from traditional speaker Lineout, and buzzers on the motherboard can be omitted.

Most of the motherboards manufactured recently conform to AC 97 specifications, attaining a set of simple and cheap sound card or 56 Kbps modem functions by opening BIOS, which is enough for users who only type the words, merely surfs the net or places little emphasis on acoustic-optic effects, however, opening the Audio or Modem functions of AC97 can consume the execution efficiency and resources of the CPU, when installing high operating efficiency and sound quality sound card or external modems, motherboards in conformity with AC 97 specifications will automatically detect external sound cards or modems.

Meanwhile, close the AMC elements on the motherboard, and let the hardware sound card/modem to take over.

#### SM Bus (System Management Bus)

SM Bus (System Management Bus) is the bus contact interface of the two signal lines designed following I2C protocol, which is a low speed interface (80KHz~400KHz) for setting of the detection, positioning, reading and writing parameters of peripheral parts in compliance with SM Bus.

Normally, computer motherboards have built-in SM Bus control circuits (SM Bus Controller) inside south bridge chipsets. The motherboard can, via SM Bus. Detect DRAM and automatically grab timing parameters (SPD) and read the parameters of hardware monitoring chips, monitor CPU, operating temperature and voltage of motherboard and motor speed (RPM) of coolant fan, etc. And, the motherboard of notebook computer detects the electrifical power index of the battery and the possibility to independently close or restart peripheral devices, parts via the SM Bus, temporarily closes peripheral devices and parts power supplies that are not used currently via the SM Bus through ACPI protocol when the entire system needs to enter power saving status to optimize power management.

#### USB (Universal Serial Bus)

USB is the computer peripheral bus standard jointly developed by computer and communication industry manufacturer such as Compaq, IBM, DEC, NEC, Intel, Microsoft and Northern Telecom, which is a so-called general-purpose serial bus. X86 motherboard was introduced in 1997. In 1999, Apple iMac also adopted USB, speeding the popularity of USB peripheral devices.

USB bus provides extension ability to medium and low speed peripheral devices. Peripheral devices such as keyboard, mouse, joystick, speaker, microphone, modem, cinematograph, through USB interface designs, can be directly connected or removed by means of hot-plugs; computers and OS may automatically detect and enable/disable the device to achieve the objectives of Plug and Play. USB has strong expansion abilities, capable of connecting at most 127 sets of peripheral devices (including USB HUB), the connection distance of each hub to device runs to 5 meters, and USB connector has a special design, which makes it very convenient to install or remove. USBv1.0/1.1 provides maximally 12 Mbps(=1.5MB/s) transmission rate; so far, the motherboards meet the specifications of version 1.1 and the newly approved version 2.0 increased transmission rate to 480Mbps (=60MB/s) , what is more, relevant interface cards, peripheral devices and motherboards have already achieved

this function and become the supporting item of future chipsets.

Hardware specification mainly includes Universal HCI (Universal Host Controller Interface) developed by Intel and Open HCI (Open Host Controller Interface) designed and opened by COMPAQ, common USB peripheral devices support these two protocols, with the differences between the two shown in table 1-8-1 below.

| The formation of the first of t |                               |                               |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|--|--|--|

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UHCI (Universal Host          | OHCI (Open Host               |  |  |  |

| Different items                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Controller Interface          | Controller Interface)         |  |  |  |

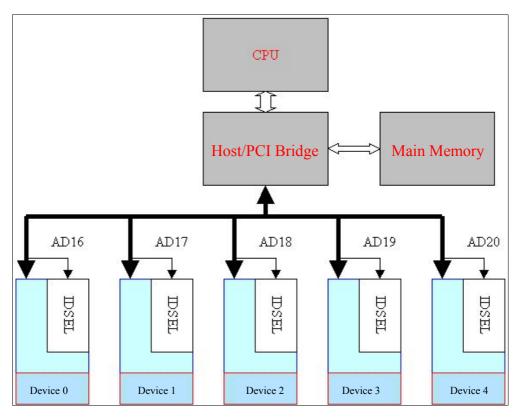

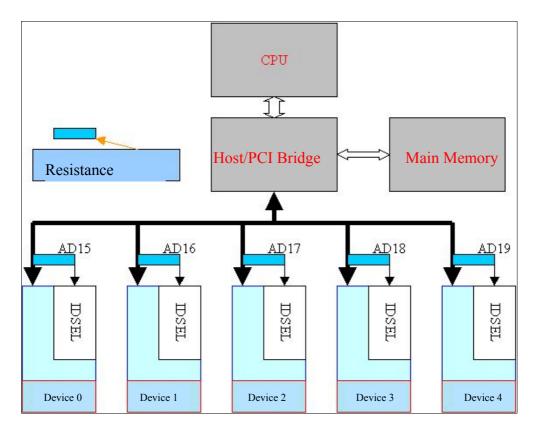

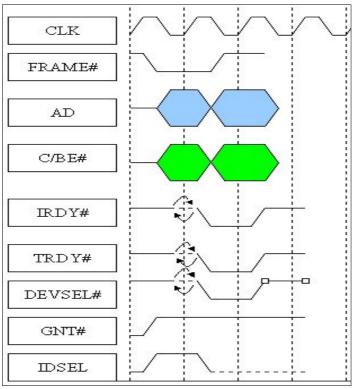

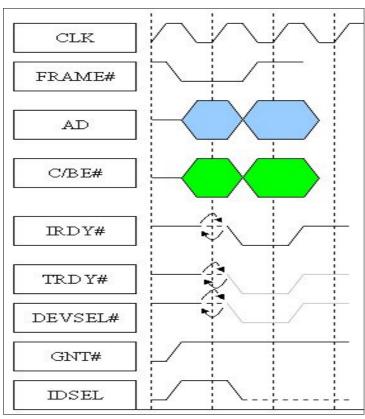

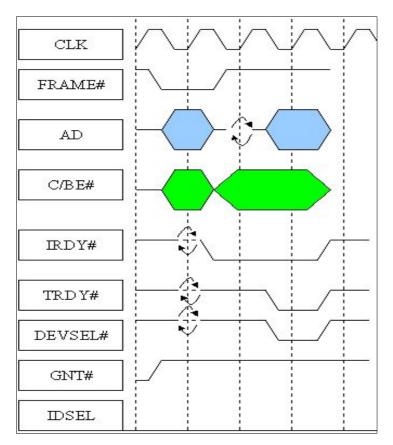

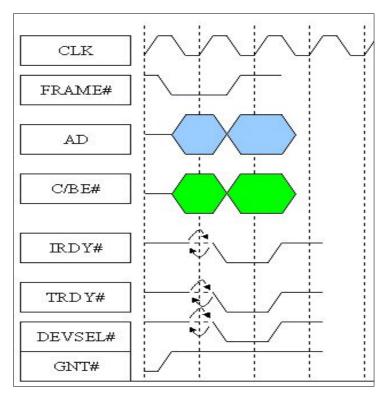

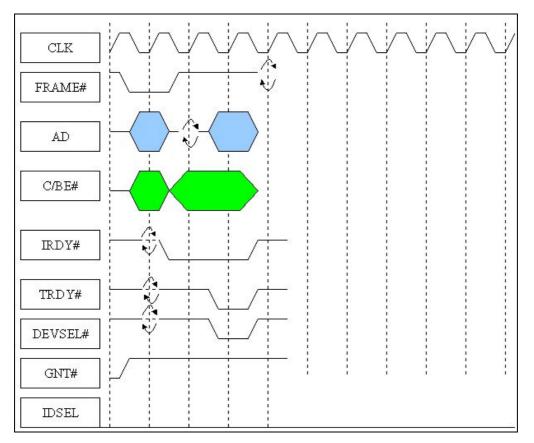

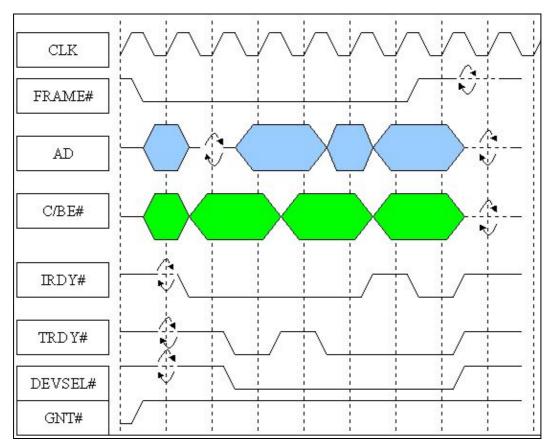

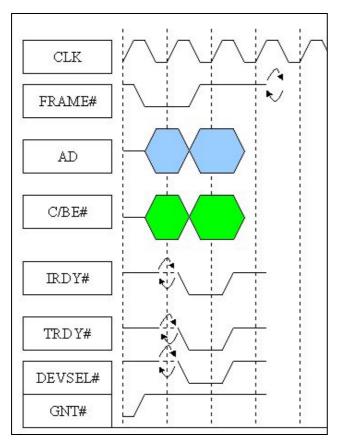

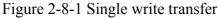

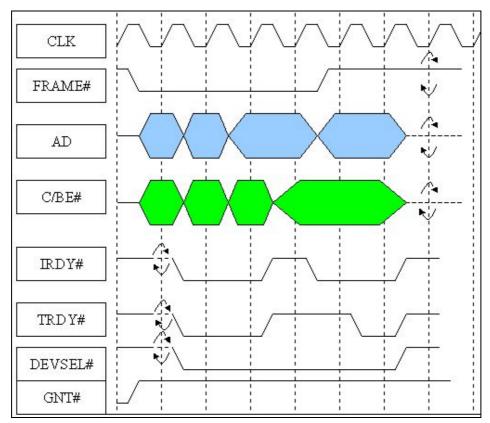

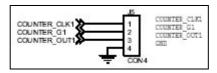

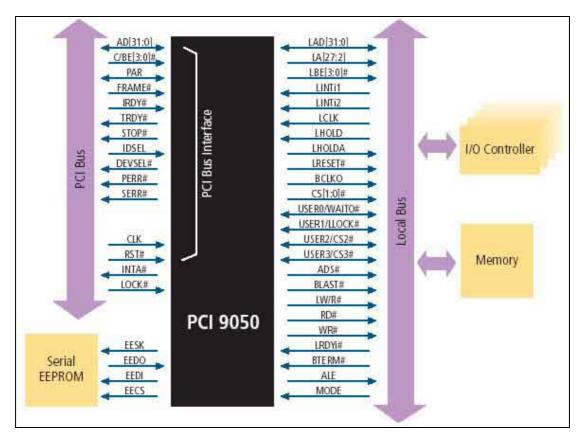

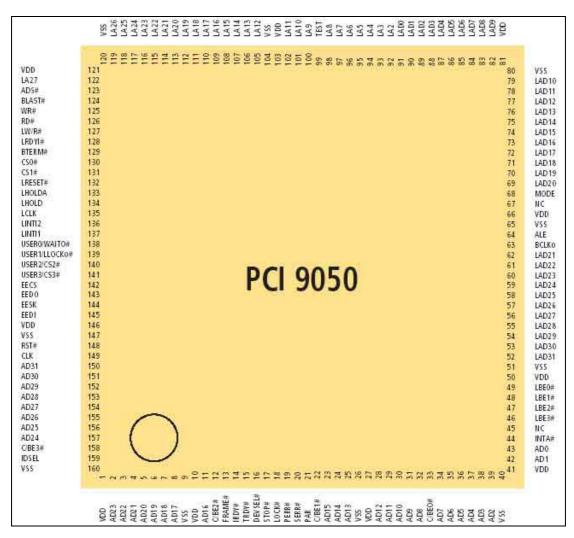

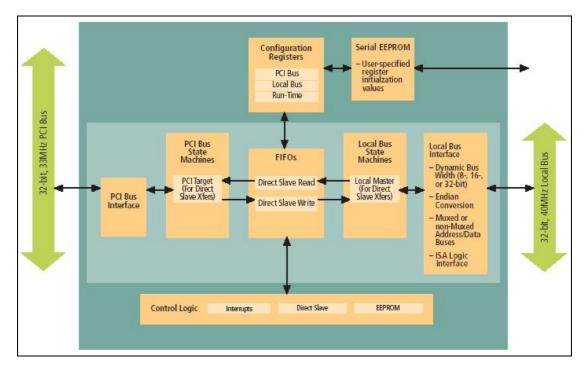

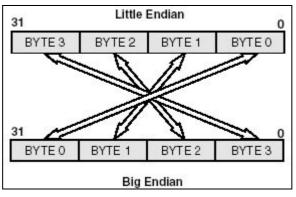

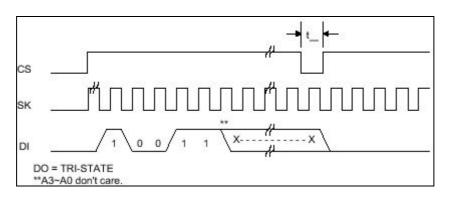

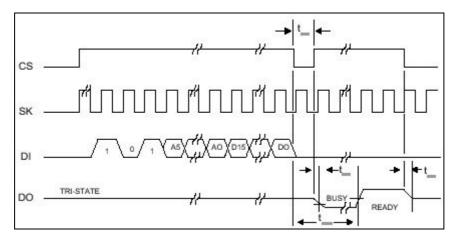

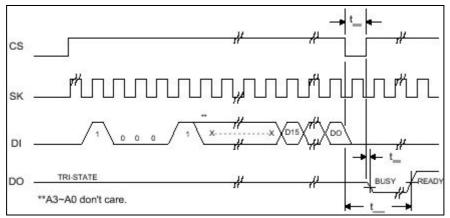

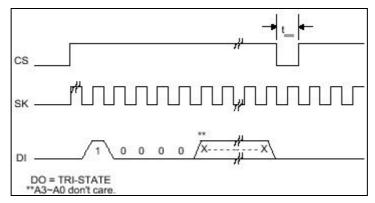

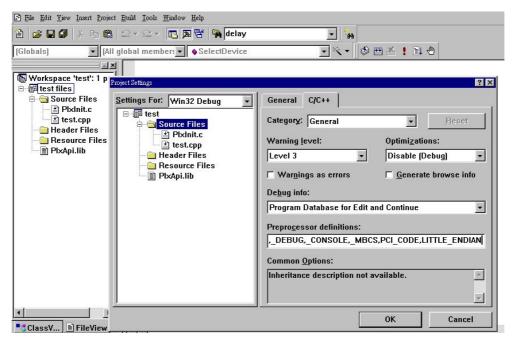

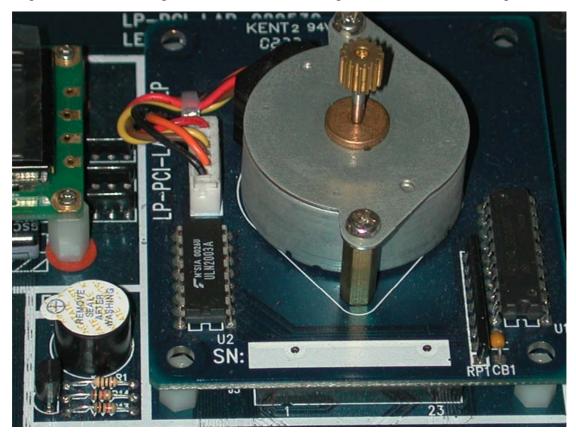

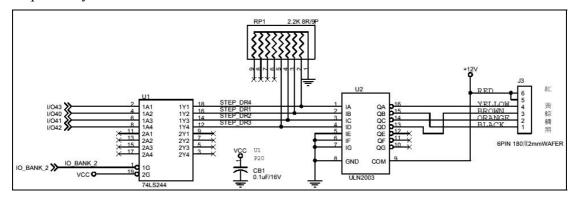

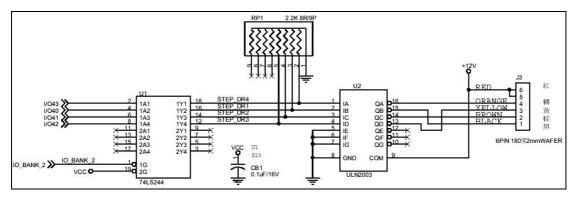

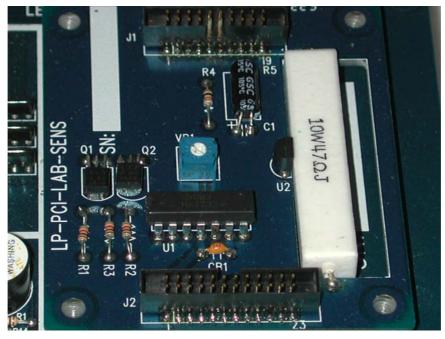

| First published                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Jan 15 <sup>th</sup> 1996     | Nov 22 <sup>nd</sup> 1995     |  |  |  |