# Logic Design and Practices

The information in this document is subject to change without notice

LEAP software products are copyrighted by and shall remain the property of LEAP ELECTRONIC CO., LTD. Use duplication, or disclosure is subject to restrictions as stated in LEAP's applicable software license.

LEAP ELECTRONIC makes no warranty of any kind with regards to this material, including, but not limited to, implied warranties of merchantability and fitness for a particular purpose, except as stated in Leap's applicable software license.

No part of this document may be copied or reproduced in any form without the prior written consent of LEAP ELECTRONIC CO., LTD.

Copyright © 2000 LEAP ELECTRONIC CO., LTD.

All Rights Reserved.

First Edition, November 2000.

By LEAP ELECTRONIC CO., LTD.

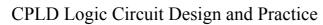

CPLD Logic Design and Practices is a trademark of LEAP ELECTRONIC CO., LTD. Other brands and product names are trademarks or registered trademarks of their respective holders.

LEAP ELECTRONIC CO., LTD. service@leap.com.tw

## Contents

### Chapter 1. Introduction to Digital Logic

- 1.1 Introduction to Digital Logic

- 1.2 Integrated Digital Logic Design Environment

- 1.3 Programmable Logic Device PLD

- 1.4 PC Aided Digital Logic Design

- 1.5 Experimental Platform

- 1.6 Evaluation and Test

### Chapter 2. Numerical System

- 2.1 Numeric Expressions

- 2.2 Numerical System Conversion

- 2.3 Numerical Complement

- 2.4 Negative Binary Number Expression

- 2.5 Binary Arithmetic Operations

- 2.6 Binary-coded Decimal (BCD) Code

- 2.7 Review

### Chapter 3. Basic Logic Theories

- 3.1 Boolean Algebra

- 3.2 Boolean Algebra Simplification

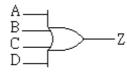

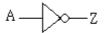

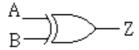

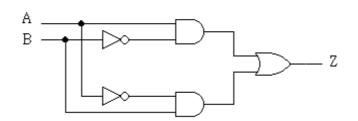

- 3.3 Logic Gate

- 3.4 Applications of Logic Gate

- 3.5 Practices

- 3.6 Review

### Chapter 4. A New Design Methodology

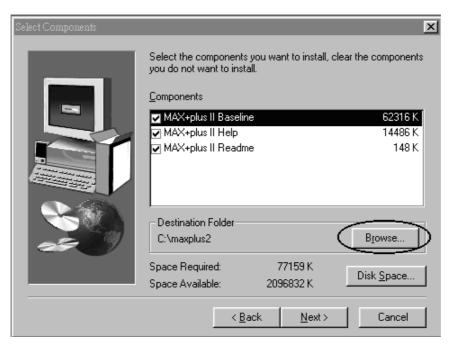

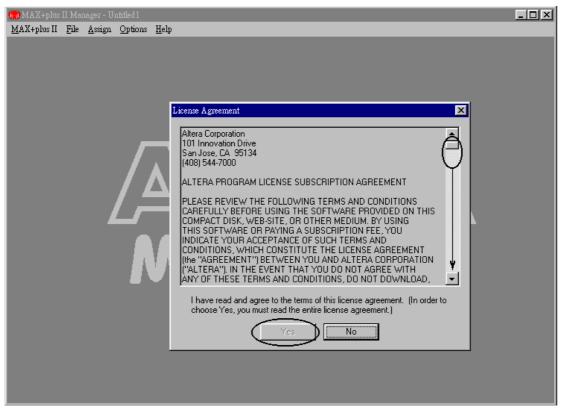

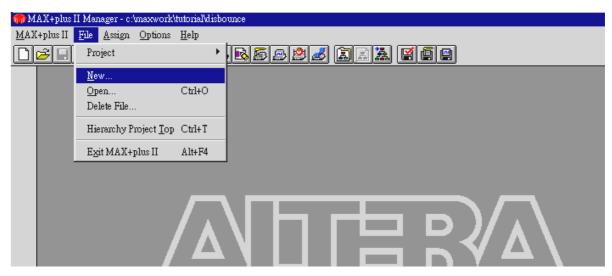

- 4.1 MAX+PLUS II Baseline Setup and Start

- 4.2 How to Use Mouse

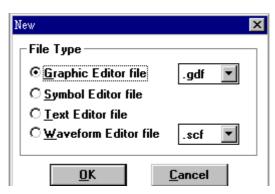

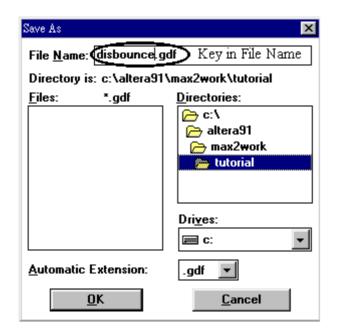

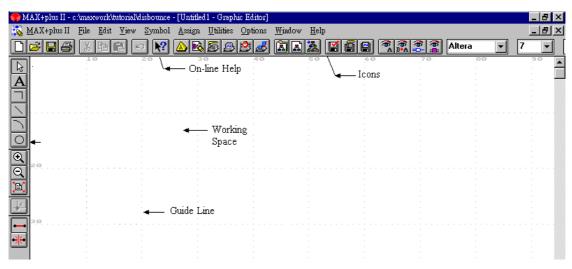

- 4.3 Graphic Entry

- 4.4 Functional Simulation

- 4.5 Floorplan and Design Compilation

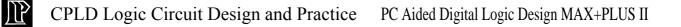

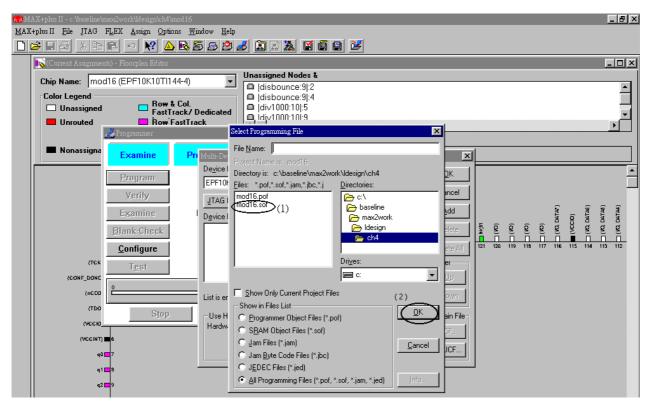

- 4.6 Device Programming and Circuit Testing

- 4.7 Use Graphic Entry to Complete LEDTEST Example

- 4.8 Review

Chapter 5. Combinational Logic Circuit

- 5.1 The Design, Simulation and Test of General Combinational Logic Circuit

- 5.2 The Design, Simulation and Test of Adder

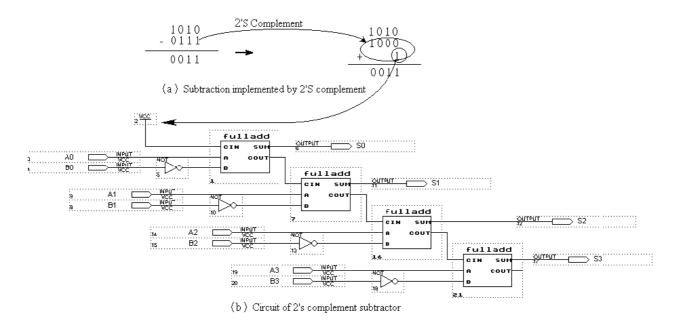

- 5.3 The Design, Simulation and Test of Subtractor

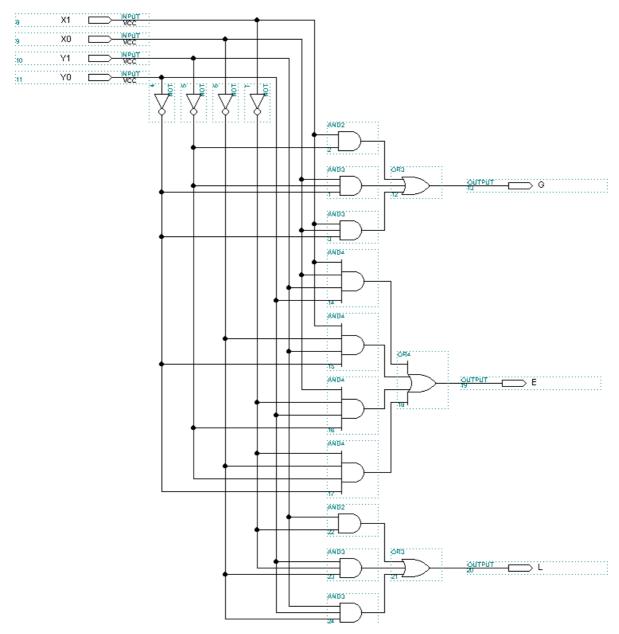

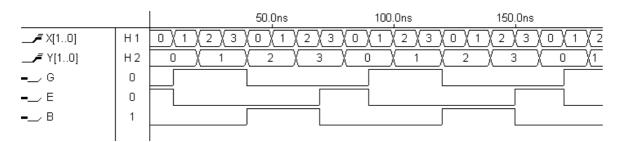

- 5.4 The Design, Simulation and Test of Comparator

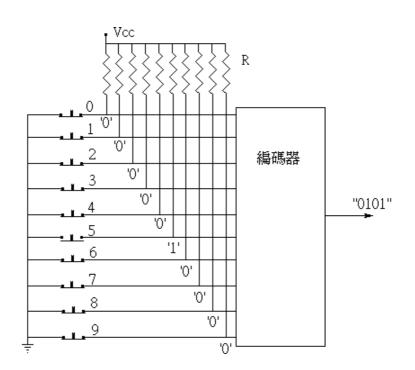

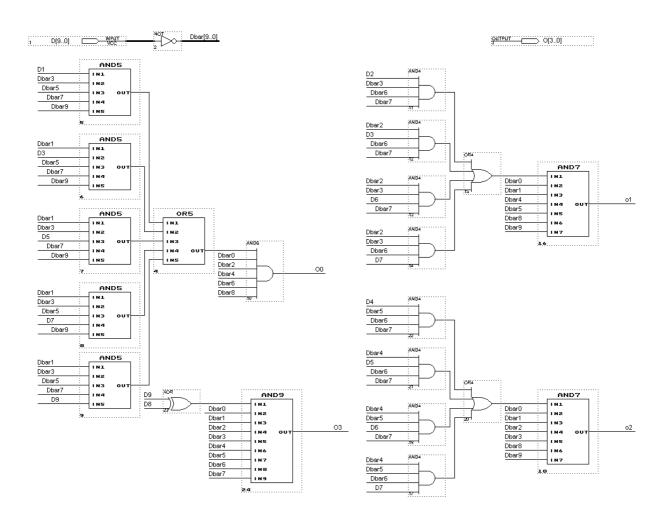

- 5.5 The Design, Simulation and Test of Encoder

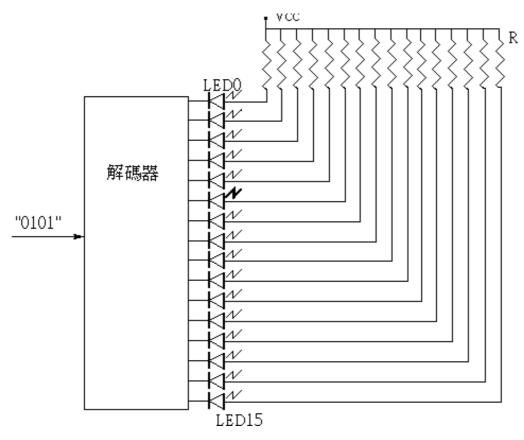

- 5.6 The Design, Simulation and Test of Decoder

- 5.7 The Design, Simulation and Test of MUX

- 5.8 The Design, Simulation and Test of DMUX

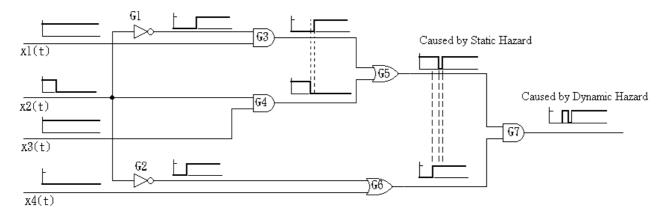

- 5.9 The Question of Harzards

- 5.10 Evaluations

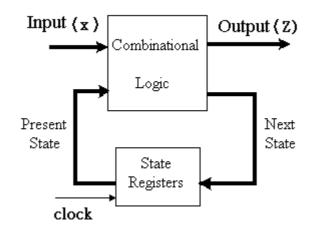

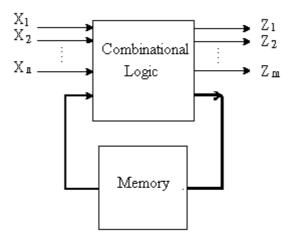

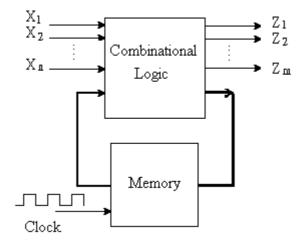

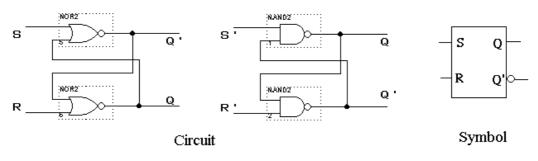

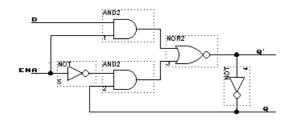

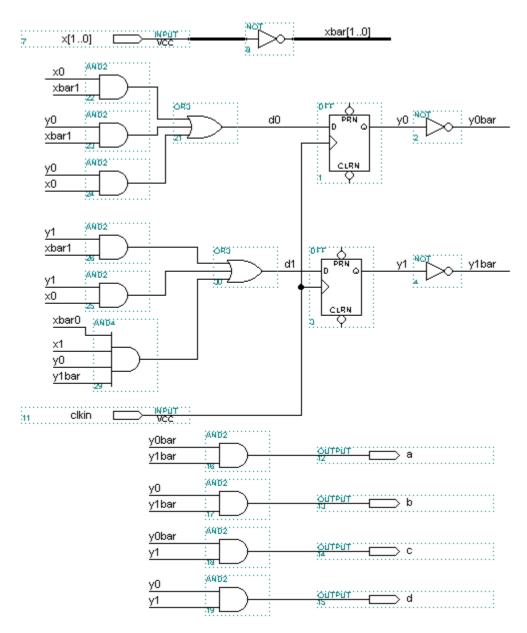

### Chapter 6. Sequential Logic Circuit

- 6.1 Basic Concept of Sequential Logic Circuit

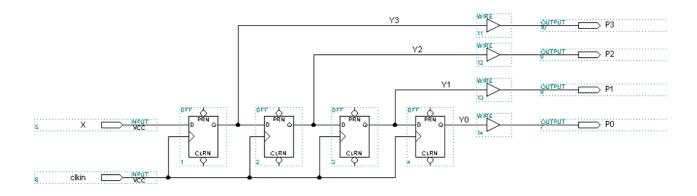

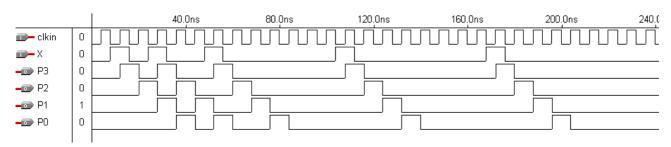

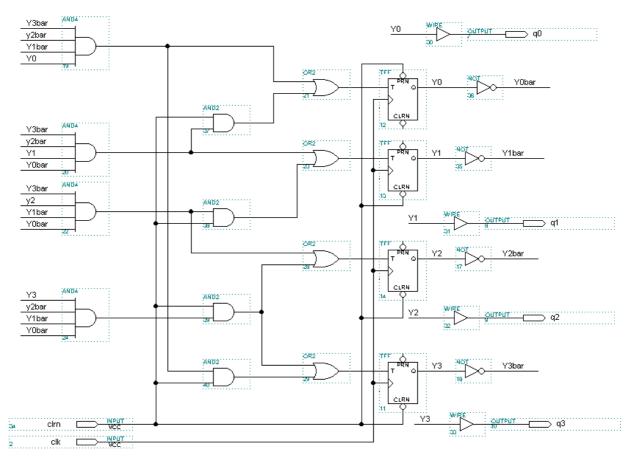

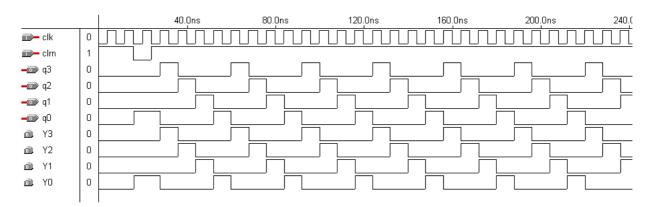

- 6.2 The Design, Simulation and Test of Synchronous Counter

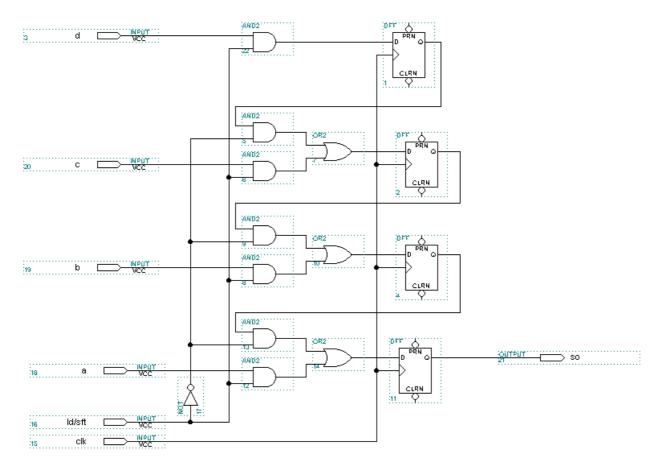

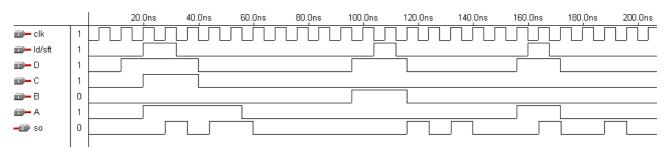

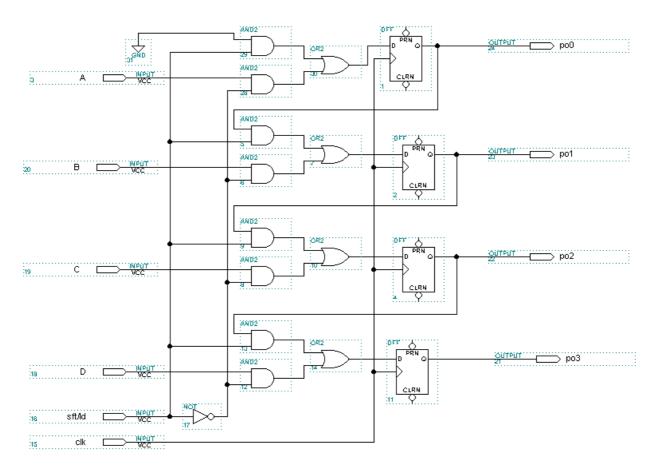

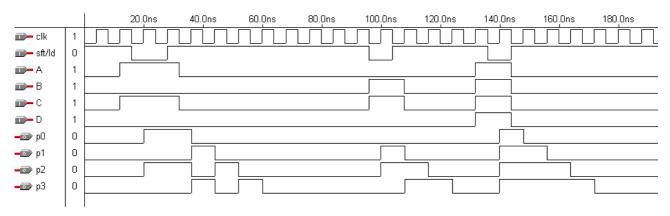

- 6.3 The Design, Simulation and Test of Synchronous Shift Register

- 6.4 The Design, Simulation and Test of Synchronous Shift Count Register

- 6.5 The Design, Simulation and Test of Asynchronous Counter

- 6.6 Evaluation

### Chapter 7. SIMPLE DESIGN EXAMPLES

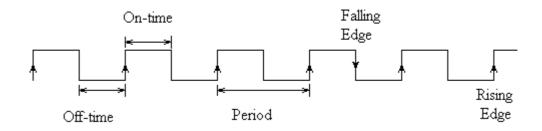

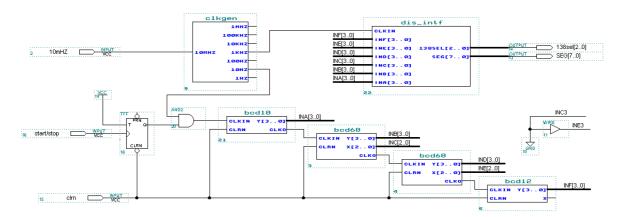

- 7.1 Frequency Generator

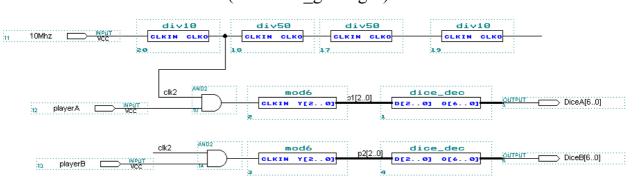

- 7.2 Simple Electronic Dice

- 7.3 Timer

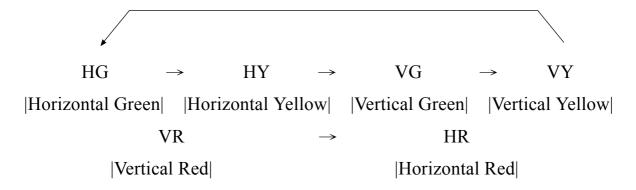

- 7.4 Simple Traffic Light Controller

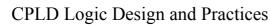

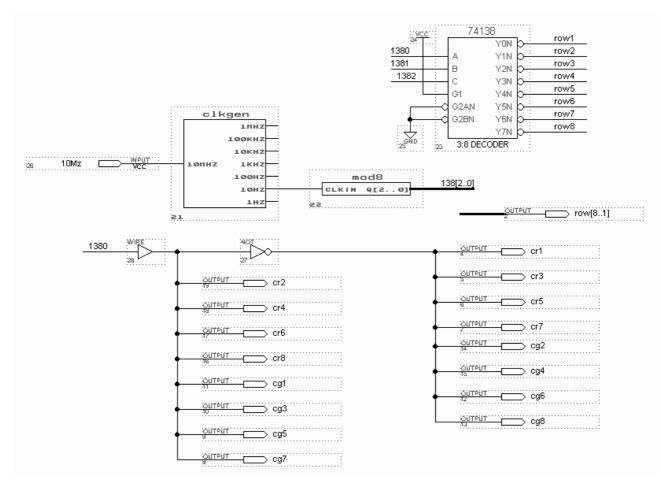

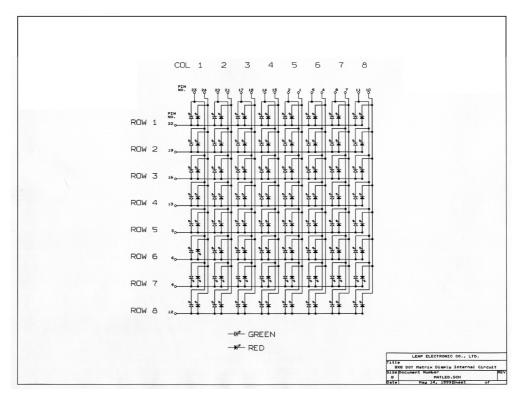

- 7.5 Dot Matrix Displayer Test Circuit

- 7.6 Keyboard Scan and Display Scan Circuit

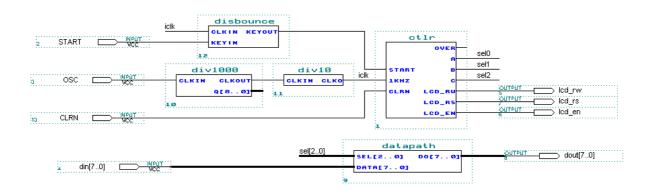

- 7.7 LCD Interface Circuit

- 7.8 Evaluations

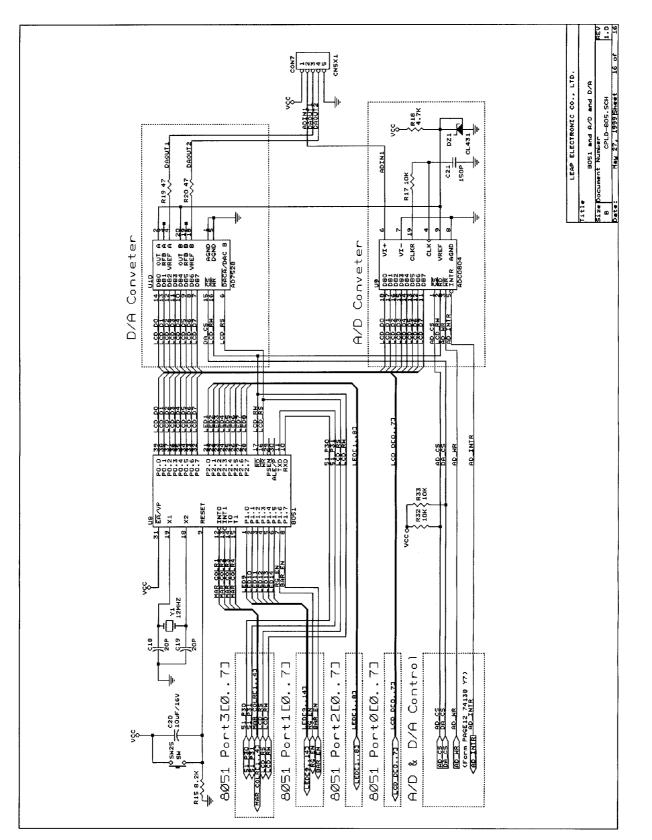

#### Chapter 8. Connecting with Analog Circuit

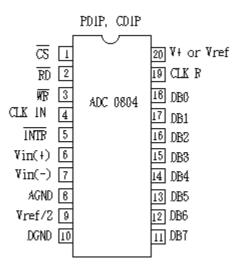

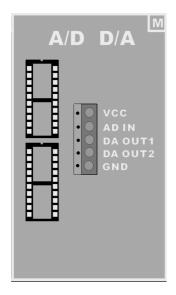

- 8.1 A/D Converter ADC0804

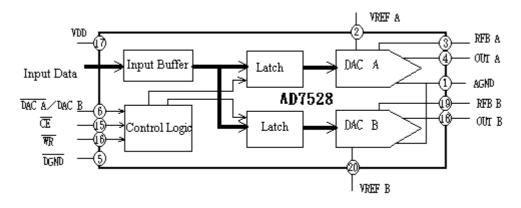

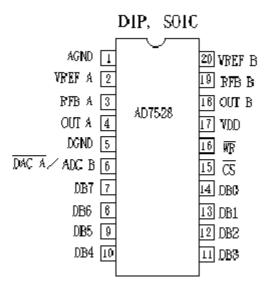

- 8.2 D/A Converter AD7528

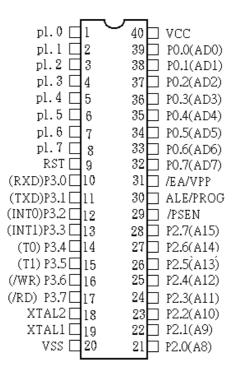

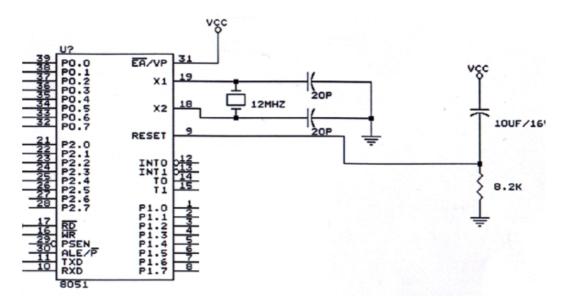

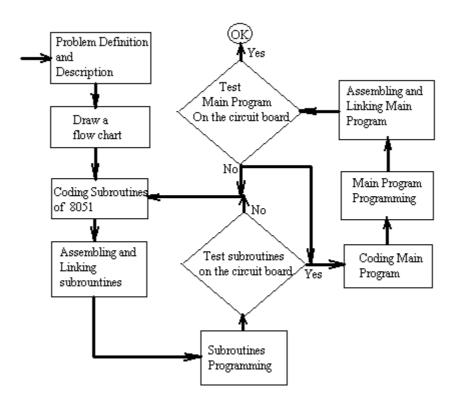

- 8.3 Single Chip 8051

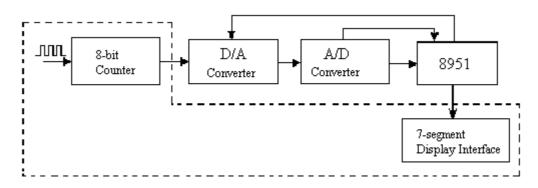

- 8.4 Design Example Connecting with ADC0804, AD7528, and 8951

- 8.5 Evaluation

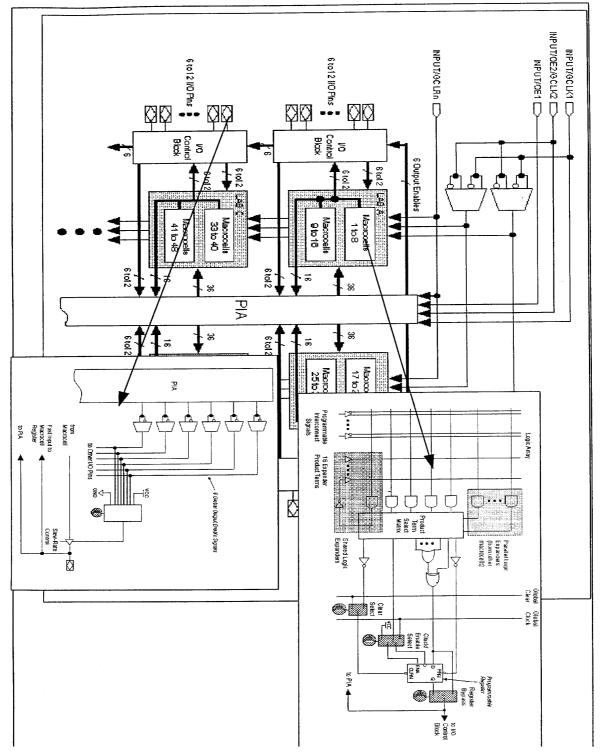

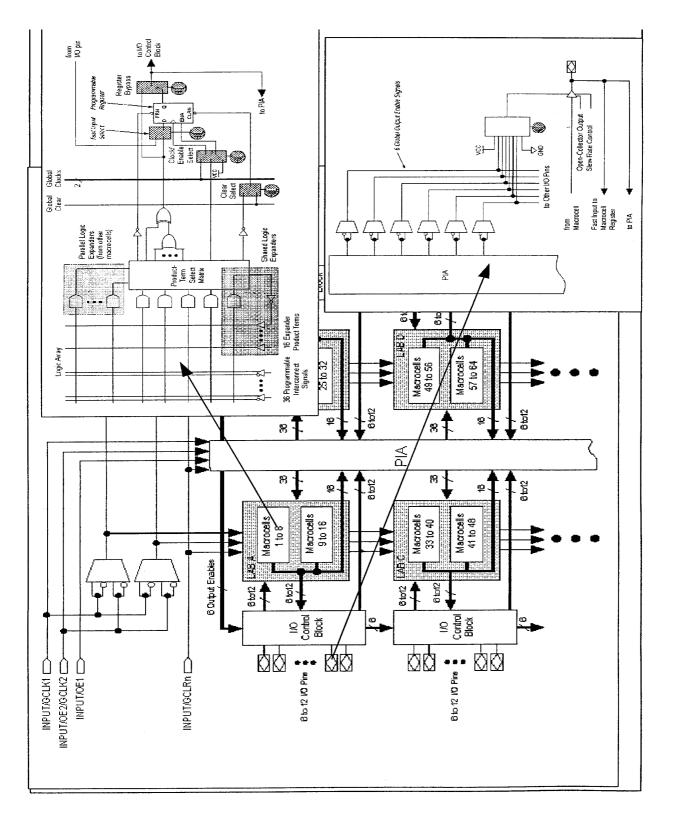

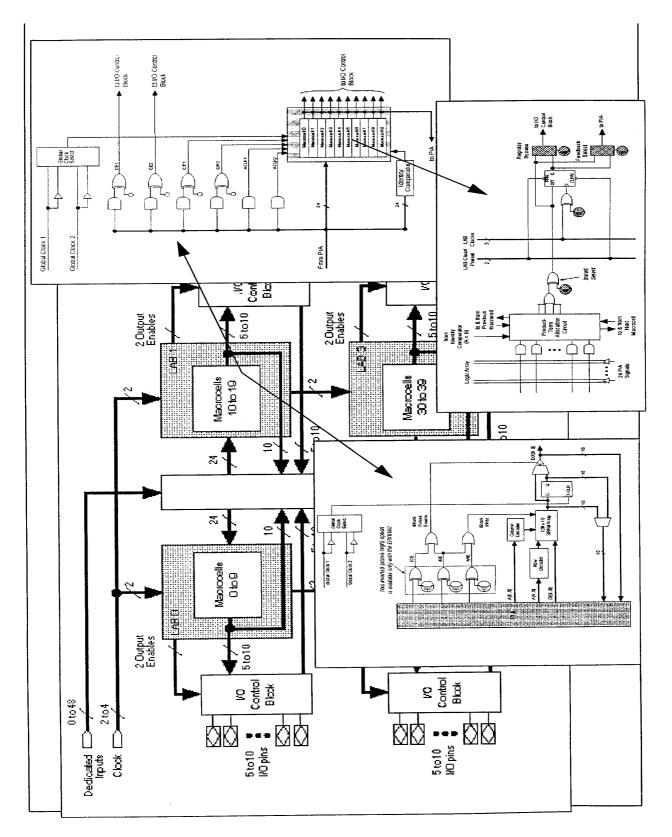

### Chapter 9. CPLD LOGIC DESIGN LAB PLATFORM LP-2900

- 9.1 Function Description to LP-2900

- 9.2 Setting up LP-2900

- 9.3 The Architecture and Circuits of LP-2900

- 9.4 Pin arrangement of LP-2900

- 9.5 Evaluations

#### Appendix A. PLD Suppliers and Main Products

- A.1 PLD Suppliers and Main Products

- A.2 ALTERA's CPLD Devices

- Appendix B. The Built-in Resources of MAX+PLUS II

- **B.1** Primitives

- **B.2 Macrofunctions**

# CHAPTER 1

# Introduction to Digital Logic

# **1.1** Introduction to Digital Logic

In general, all physical quantities in nature such as temperature, humidity, length, speed, and time are continuously changing. We call these continuously changing signals as "analog" signals. In contrast to analog, there is a discrete signal called "digital" signals. A signal processing system with use of analog signals is called "analog system". Signals in this kind of system continuously fluctuate over time between high and low voltages. For example, signals are changing from -10 voltage to +10 voltage. Similarly, a signal processing system with use of digital signals is called "digital system", and signals in this system can only be considered either on or off, high or low values. For example, signals can change either 0 voltage or +5 voltage.

From above, we could know there are two systems to process signals. One is analog system and the other is digital system. Generally, a digital system comes with more benefits than analog. It is programmable, faster, precise, and flexible. Besides, as the signals are discrete but not continuous, a digital system can be less affected by the changes of elements' natures such as the problem of a worn-out transistor. Those are the reasons why digital systems are greatly adopted in the world.

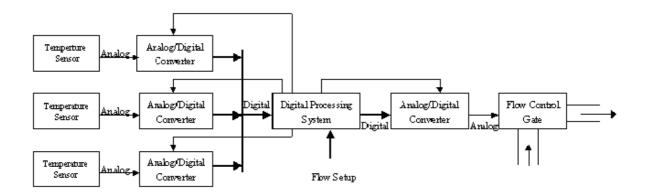

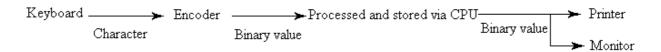

For sure, all physical quantities in nature are shown in the form of analog signals. They are measurable, visible and controllable. If we would like to take the advantages of digital systems, we have to transform signals from analog to digital and process by digital systems. The transforming process is as below:

Analog Signals

Analog Signals

Digital Signals

Physical Quantity

→Sensor

→Analog-to-Digital Converter

→Digital Processing System

Sensors can transform the natural physical quantities into electronic signals such as voltage or current signals that are still analog signals. Electronic signals will then been transformed into digital signals by Analog/Digital Converter. Actually, Analog/Digital Converter is responsible for sampling and quantization. Sampling is to take the value of a physical quantity at one point and then mark it as a digital number, and this is what we called "Quantization". Processed digital signals will be

transformed into analog signals in some circumstances to have better control on some objectives such as flow control gates, fans, and heaters etc. The transforming process is as below:

| Digital Signals                                      | Digital Signals                                   |

|------------------------------------------------------|---------------------------------------------------|

| Digital Processing System $\rightarrow$ Digital-to-A | nalog Converter $\rightarrow$ Controlled Machines |

Figure 1.1, it is the flow control diagram for a chemical factory. A/D Converter, Digital Processing System, and D/A Converter are the key points in Figure 1.1 as well as in this book. To introduce digital processing systems, we will discuss the topic from the basic theory first, including Numeric System (Chapter 2), Boolean algebra (Chapter 3), and then Basic Gate (Chapter 3), combinational logic (Chapter 5) as well as Sequential Circuit (Chapter 6). More over, we will talk about A/D Converter and D/A Converter in Chapter 8. In the rest of the Chapter 2, we will introduce a new logic design environment called "Integrated Digital Logic Design Environment". **This integrated environment will greatly give us logic design and simulation**. In Chapter 4, we will further discuss how to set up and use the EDA tool, MAX+PLUS II.

Figure 1.1 A Flow Control Diagram for a Chemical Factory

# **1.2** Integrated Digital Logic Design Environment

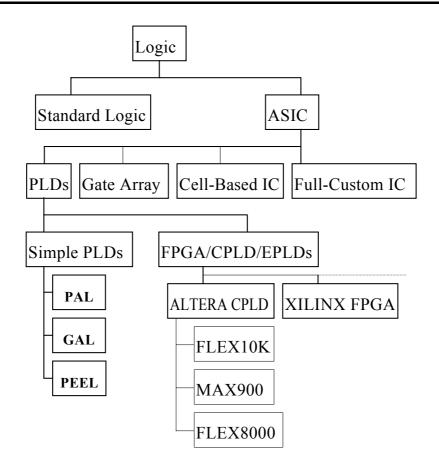

Currently, engineers can use two different chips to make PCB (Printed Circuit Board) when they design circuits. One is standard/discrete logic such as TTL/COMS 74/54 family; the other is ASIC (Application-Specific Integrated Circuits). ASIC shown in Figure 1.2 can be divided into 4 different catalogs: PLD (Programmable Logic Devices), Gate Array, Cell-Based IC, and Full-Custom IC.

Standard logic is TTL/CMOS (e.g.: 74/54 family) that comes with a specific function. This is the first device to make digital logic circuits and digital systems in history. As the needs for digital circuits are more and more complicated and the new technologies are developed faster than before, standard circuits gradually cannot satisfy customers, and, as a result, a new market is there for Gate Array, Cell-Based IC, and Full-Custom IC. All the devices use different ways to design circuits and different process to produce circuits. For a programmable logic device (PLD), it is an integrated circuit that has user-configuration functions, including Boolean expression or registered function etc, to customize the circuits and meet customer's needs. Those functions make PLDs quite different than TTL/CMOS standard devices. As long as the elements have the user-configuration functions, they are PLD elements, including 3 different catalogs: 1.) PAL/GAL with simple functions, low capacity, and low pin counts, 2.) FPGA (Field-Programmable Gate Array) with high capacity, higher pin counts, and 3.) CPLD (Complex PLD) with high capacity and high pin counts. Those different PLDs have their own different structures and internal-memory-type design technologies. Depended on requirements, we could choose the right devices. PAL is a simple PLD, which has gate counts from 100 to 1000 and IC pin counts within 28-pin. It is an old process with bipolar procedure, can only write data once, and cannot delete old data. Its advantage is faster speed, but its disadvantage is more electrical consumption. GAL, another simple PLD, uses CMOS as its process. It can rewrite data and has less electrical consumption. However, its operating speed is slower than PAL relatively.

Figure 1.2 Catalogs of logic devices

FPGA/CPLD process is CMOS. Currently there are five techniques to produce FPGA/CPLD: EPROM, EEPROM, FLASH, SRAM and Anti-Fuse. FPGA has higher density. Compared with CPLD, it uses less logic gates and focuses on registers. However, its routing is complicated, causing the problems of varying and longer timing delay. For new comers or students, they definitely think FPGA is more difficult and have to study harder and longer to understand it. Currently, XILINX, Actel, Atmel and AT&T are the key suppliers, and, among them, XILINX has greater market share and is the biggest FPGA supplier in the market. For CPLD, it cans multi-erase data, program data, and fixed delay. It also allows users to apply and design easily. The main suppliers of CPLD include AMD, ALTERA, Lattice, Cypress, and ICT etc. Among them, AMD and ALTERA are the two key players in the market.

As the adoption of higher density and new process of PLD, the prices are gradually decreasing, and, as a result, PLD has given consumers higher-density, more effective,

and cheaper devices than standard logic. In another words, we could put all TTL/COMS standard circuits from a big board to a small piece of CPLD. It reduces room for a big board and time for welding process, and speed the circuit up significantly. Therefore, PLD has greatly been seen as a "super star".

Table 1.1 is the comparison for PLD, Standard/Discrete Logic, and Full-Custom IC. Clearly, PLD has the great advances in speed, density, price, developing time, modifiability, prototyping, development tools, integrity, and time to market.

| Requirements | PLD             | Discrete Device | ASIC             |

|--------------|-----------------|-----------------|------------------|

|              |                 |                 | (Full-Custom IC) |

| Speed        | Very Fast       | Slow            | Very Fast        |

| Density      | High            | Low             | Very High        |

| Price        | Cheap           | Expensive       | Very Cheap       |

| Developing   | Short           | Proper          | Long             |

| Modifiabili  | Very Flexible   | Proper          | Very Inflexible  |

| Prototyping  | Very Easy       | Very            | Very Difficult   |

| Tools        | Easy Access and | Not             | Not Expensive    |

| Integrity    | Very Small      | Very Big        | Very Small       |

| Time to      | Short           | Proper          | Long             |

Table1.1 Comparison of logic devices

# **1.2.1 Techniques of Traditional Digital Circuit Design**

As we mentioned before, Standard/Discrete Logic or ASIC can be used to make circuit board. The function of Full-Custom IC is fully user-defined, but Gate Array is a semi-product and therefore its function is defined based on this. For Cell-Based IC,

its function is to use well-defined cells in a cell base to complete circuit design. Usually, when engineers use these kinds of ASIC chips or even add with some of standard logic to design circuit boards, they are making PCB (Printed Circuit Board) samples directly. In another words, after completing circuit designs by computers, we will assign a third party to produce and weld all elements, or only ask a third party to weld SMD (Surface Mounted Device) with high pin counts and take the rest of the production procedures by ourselves. We might add/decrease elements to/from sample version 1, and have line jumping or line cutting and testing to have more correct sample boards. After completing the testing for sample version 1, we then assign a third party to produce sample version 2, and back to test it again. To have finalized circuits, we might have sample version 3 or version 4 if needed. If all correction has been done and all the requirements are met, the circuit board development is completed. We could start mass production in next. These kinds of circuits are mainly for digital system circuit designs. Currently, most of R&D in high tech industries uses the ways to design and produce new circuits.

The traditional ways of the design of digital logic circuit for standard logic, which is greatly accepted by the public, is as follow:

- > Design circuits on the papers.

- > Weld or wire all elements by practice board.

- Test circuit board by the tools such as multifunctional meter, logic probe, oscillator display, and functional generator.

- Correct circuit designs and circuit boards by adding or decreasing elements and by line jumping and line cutting testing.

- Assign a third party to produce circuit sample boards; after testing and correcting sample boards, start mass production.

Designing circuits on papers is very ineffective and inefficient. It is not easy to edit and make a change on papers. It is also unattractive, time consuming, and not easy to store. Except engineers having great experience in circuit designs, without scientific verification, there will definitely have a great of mistakes in designs. Moreover, workers use practice board to weld or wire all elements. It is going to make the job more complicated, time consuming, and defective. In order to weld all the elements, the size of a board used for standard logic very big. It is hard to decrease the board size, and, thereafter, against the market trends requiring light and small circuit boards. As Standard logic is not going to be on production lines, we could predict that the way to design circuits will not be accepted by the market soon. It is a fact. It is the trend in the market.

# 1.2.2 Integrated Digital Logic Design Environment

Because PCs functions are more and more, memory size is larger and the prices are lower than before, the world PC users are increasing significantly. As a result, electronic design automatic (EDA) is greatly available in the market. The EDA software can be used in PC platform. EDA software offers the functions including graphics, texts, and waveform entry. It offers a great user-friendly environment to modify designs and manage files and we called this is the scientific ways to manage files. EDA software also gives users the environment to scientifically verify circuits: functional simulation and timing simulation. With the two simulations, new comers or less experiencing engineers almost can precisely complete the circuit designs.

With the increase of the high-density requirement and the adoption of new process, PLD prices are decreasing gradually. Compared with standard logic, PLD, consequently, can give users better devices with higher density, more efficiency, and cheaper prices. This allows us to use programmable CPLD devices with SRAM technology to design an experimental platform. Except SRAM CPLD devices, this platform also has power, PC downloading interface, and I/O elements such as LED, seven segments display, buzzer, clocks, switches, pulse switches, 4×3 keyboard, 8×8 dot matrix display, LCD display, and A/D & D/A circuit modules. The main purpose of the platform is to offer a simple and accessible environment to verify circuits and to reduce the time of circuit design. To perform the process, we have to download the circuits to the SRAM CPLD devices in the platform first, and then give required clock or input signals, inspect the results to ensure if the circuits meet specifications.

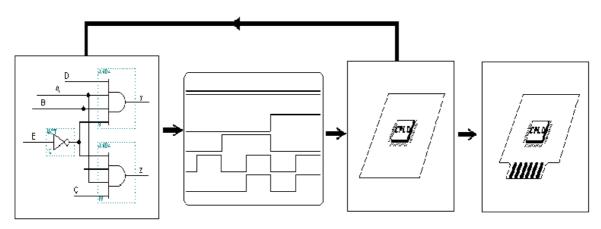

To integrate PCs, EDA software, and experimental platform, we will briefly introduce the general flow of integrated digital logic design in Figure 1.3. We use EDA software on PC to make design entry and to simulate circuits. To verify the designed circuits, we need to download "Configuration Bits" to SRAM CPLD devices in platform by the cables connecting between PC and the platform. If there are still defects after testing, we go back to the previous steps: modifying the designs, re-doing the simulation, downloading the circuits and re-testing the circuits until correct. After circuits are finalized, we then could produce the circuits.

Figure 1.3 General flow of integrated digital logic design

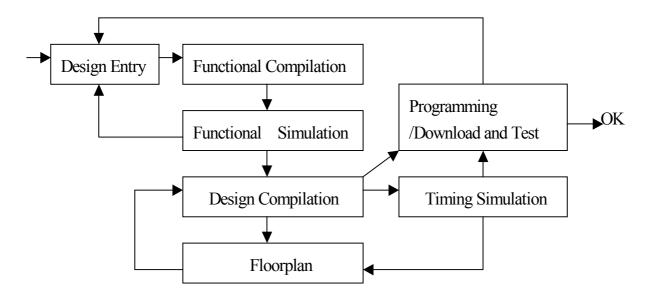

Figure 1.4 details the flow of integrated digital logic circuit design. For this flow, we will briefly discuss in Section 1.4, and have further discussion with real examples in Chapter 4. Table 1.2 to 1.5, we will compare the differences between traditional and integrated logic circuit designs in terms of tools, elements, circuit design flow, and study requirements.

Figure 1.4 Flow of integrated logic circuit design

| T 1 1 1 0   | a :        | 0 1 1 1           | 1            |              |             | (1 , 1)    |

|-------------|------------|-------------------|--------------|--------------|-------------|------------|

| Table 1.2   | Comparison | of traditional an | d integrated | l digital lo | ogic design | (by tools) |

| 1 00 10 1.2 | Companyou  | or maareronar an  |              |              |             | (0,0010)   |

| Types                     | Tools                                                                      |

|---------------------------|----------------------------------------------------------------------------|

| Traditional Digital Logic | <ul> <li>Multifunctional Meter</li> </ul>                                  |

| Design                    | <ul> <li>Oscillator Display</li> </ul>                                     |

|                           | Logic Probe                                                                |

|                           | Logic Analyzer                                                             |

|                           | <ul> <li>Experimental board and Wiring Tool or<br/>Welding Iron</li> </ul> |

|                           | o                                                                          |

| Integrated Digital Logic  | <ul> <li>Multifunctional Meter</li> </ul>                                  |

| Design                    | <ul> <li>Oscillator Display</li> </ul>                                     |

|                           | Logic Probe                                                                |

|                           | PCs and EDA Design Tools                                                   |

|                           | Experimental Platform                                                      |

| Types                     | Elements                        |

|---------------------------|---------------------------------|

| Traditional Digital Logic | Resister                        |

| Design                    | Capacitor                       |

|                           | LED, Seven Segment Display, Dot |

|                           | Matrix Display, LCD             |

|                           | SSI, MSI, LSI                   |

|                           | A/D, D/A                        |

|                           | Transistor, Amplifier           |

|                           | VLSI Chips                      |

|                           | Wild Spread PCB                 |

|                           |                                 |

| Integrated Digital Logic  | Resister                        |

| Design                    | Capacitor                       |

|                           | LED, Seven Segment Display, Dot |

|                           | Matrix Display, LCD             |

|                           | PLD components                  |

|                           | A/D, D/A                        |

|                           | Transistor, Amplifier           |

|                           | VLSI Chips                      |

|                           | Compacted PCB                   |

|                           |                                 |

Table 1.3

Comparison of traditional and integrated digital logic design

(By elements)

| Table 1.4 Comparison of traditional and integrated digit | tal logic design |

|----------------------------------------------------------|------------------|

|----------------------------------------------------------|------------------|

|                           | <br>- · ·                                            |

|---------------------------|------------------------------------------------------|

| Types                     | Circuit Design Flow                                  |

| Traditional Digital Logic | Specification Definition                             |

| Design                    | Circuits Design on Papers (Only<br>Schematic Entry)  |

|                           | Chips Selection                                      |

|                           | PCB Welding or Wiring                                |

|                           | Circuit Testing and Modifying                        |

| Integrated Digital Logic  | Specification Definition                             |

| Design                    | Data Input (Including Schematic, Text, and Waveform) |

|                           | Design Compilation                                   |

|                           | Design Simulation                                    |

(By circuit design flow)

| Table 1.5 | Comparison of traditional and integrated digital logic design |

|-----------|---------------------------------------------------------------|

|           | (By study requirements)                                       |

| Types                     |                                                                                                                                                                                                                                  | Study Requirements             |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|

| Traditional Digital Logic |                                                                                                                                                                                                                                  | Great Experience and Knowledge |  |

| Design                    |                                                                                                                                                                                                                                  | Needed                         |  |

|                           | <ul> <li>Great Experience and Knowledge<br/>Needed</li> <li>Use of Various Equipment</li> <li>Time Consuming and Great Experience<br/>Requirement for PCB Welding or<br/>Wiring</li> <li>Problems with Keeping Design</li> </ul> |                                |  |

|                           | Time Consuming and Great Experient                                                                                                                                                                                               |                                |  |

|                           | Requirement for PCB Welding or                                                                                                                                                                                                   |                                |  |

|                           |                                                                                                                                                                                                                                  | Wiring                         |  |

|                           |                                                                                                                                                                                                                                  | Problems with Keeping Design   |  |

|                           |                                                                                                                                                                                                                                  | Information                    |  |

| Integrated Digital Logic<br>Design | Less Experience and Knowledge<br>Needed                                                                                                                                                 |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | Decrease of Using Various Equipment                                                                                                                                                     |

|                                    | Time Saving, Ease of Understanding<br>the Knowledge, and Good Information<br>Maintenance, Reuse of Information,<br>and Convenience of Modifying Design<br>Data by Computer Aided Design |

|                                    | Decrease of PCB Welding or Wiring                                                                                                                                                       |

To the integrated digital logic design flow, we have following conclusions:

- 1. EDA computer aided design can effectively help us to learn new knowledge and save time. It can also keep design information well; reuse and modify the information easily.

- 2. It decreases the work of welding or wiring circuit boards. It also reduces defects from human factors.

- 3. It has "Design Entry  $\rightarrow$  Circuit Simulation  $\rightarrow$  Downloading Testing" streamline process, which is just right to today faster circuit development.

- 4. By performing the above process, PCB samples are almost completed and finalized, and have fewer defects. We then could decrease the possibilities to reproduce another samples and therefore shorten the developing time.

- 5. Because CPLD has great programmability, we could make samples and perform "Design Entry → Circuit Simulation → Downloading Testing" process at the same time. It helps us to shorten or avoid the time to wait for samples. (Note: LP-2900 is completed by this development mode.)

- 6. Because CPLD has great higher gate counts which can integrate many logic chips in a small board.

The integrated digital logic design flow can also be lectured in school. Instructors can introduce theories first, talk design and simulation next, and then prove the theories by downloading and testing circuits. Students will well understand the theories after taking the course. Each of theories or design examples can been proved by testing in class immediately. Students will have great impression and understanding, and so feel confident, willing to study further knowledge about digital logic. Unlike the flow of integrated digital logic design, the flow of traditional digital logic design will not have IC simulation after the introducing theories and design examples. It requires users to weld circuits or put components on breadboards by her/himself to test circuits. Welding process is very time consuming, plus bad connection in breadboards and human factors can cause faulty problems and prolong the processing time. Student might feel discouraged and only understand one or two simple logic designs and practices. If so, there will have no hope and improvement for our digital circuit design. Isn't it?

# 1.3 Programmable Logic Device - PLD

In previous section, we have mentioned that engineers could use Standard/Discrete Logic (e.g. TTL/COMS 74/54 family) and ASIC to make circuit boards. ASIC shown in Figure 1.2 can be divided into 4 different catalogers: Programmable Logic Devices, Gate Array, Cell-Based IC, and Full-Custom IC. However, higher performance, high-density logic integration, greater cost-effectiveness, and short development cycle are the four key factors considered by customers to buy chips. "Higher performance" is clock speed rate or coherent signal propagation, and is closely related to circuit process and architecture. For "high density logic integration", it means that the device can integrate more logic gate counts in same area. This is one of the goals when engineers design circuits in the second run. They try to put more circuits in a smaller area to reduce PCB space and cost. "Greater cost-effectiveness" is of performing the same performance of circuit with less expense. "Short development cycle", it obviously means to shorten development period, including the stages: design entry, compiling process, simulation, and programming as well as PCB testing. Definitely, the shorter developed time the better to catch up time to market. From the comparison shown in Table 1.1, PLD has greater advantages than Standard/Discrete Logic for all comparison items, but is inferior to Full-Custom IC in density and cost.

Programmable logic device (PLD) is a kind of IC. It has a user-configuration function, which allows users to customize their logic functions including Boolean expression and/or registered function. It is quite different from TTL/COMS standard logic that only provides fixed functions in early stage. As PLD density is increasing and the new process is adopted, prices are gradually decreasing, and therefore PLD has been able to offer higher density, higher performance, and lower prices than standard logic. It is becoming very valuable in the market.

All devices that come with user-configuration functions can be seen as PLD devices. They include PAL/GAL devices with the simple, low-density, low-pin-count features, field-programmable gate array (FPGA) with high-density and high-pin-count features, and complex PLD with high-density and high-pin-count feature. Those PLDs have their own different internal structures and internal memory design models. It is depended on the needs and the sizes of the circuits to select devices properly. To PAL, it is a simple programmable logic device, which has gate counts from 100 to 1000 and IC pin counts within 28 pins. Bipolar process is used for PAL, which is an old product and can only record once and cannot delete old data. PAL has the potential of faster speed, but it can consume more electric power. For GAL, it is also a simple PLD, but is mad CMOS. GAL can rewrite and delete data many times. Its speed rate is slower but power consumption is less than PAL.

FPGA and CPLD are made by CMOS. Currently there are five techniques used in FPGA/CPLD, and those are EPROM, EEPROM, FLASH, SRAM, and Anti-Fuse. FPGA has higher density. The difference from CPLD is of that FPGA has less logic gates and focuses on registers. However, FPGA routing is complicated, causing the unfixed and longer timing delay. For students, it definitely is not easy to understand, and has to take longer to study the knowledge. Currently, there are some key suppliers in the market such as XILINX, Actel, Atmel, and AT&T. Among them, XILINX is the biggest supplier having the greatest market share in the market. CPLD, on the other hand, can rewrite and delete date unlimitedly and fix timing delay. It is also easy to use and make designs. The key CPLD suppliers include AMD, ALTERA, Lattice, Cypress, and ICT, etc. Among them, AMD and ALTERA are the two biggest suppliers in the market. (See Appendix A - PLD Suppliers and Main Products.)

Presently, PLD is applied in telecommunications such as mobile phones and radio bases, etc. It is also used in data communication network such as LAN, ATM, and

printers as well as scanners. For sure, it will be promoted into TV game and educational markets in the future.

PLD is constructed by configuration cell, logic cell, and interconnect. Configuration cell is a kind of memory. Engineers can program the cell to remember the connection processes between I/O pins and logic cells, between logic cells and logic cells, and between logic cells and interconnect. The process of those configuration cells is called "technology", and all current PLD application technologies are listed in Table 1.6.

|              | -               |                  | -           |          |

|--------------|-----------------|------------------|-------------|----------|

| Technologies | Re-configurable | Erase Methods    | Types       | Security |

| EPROM        | Yes             | Ultraviolet Ray  | Nonvolatile | Yes      |

| EEPROM       | Yes             | Electrical Erase | Nonvolatile | Yes      |

| FLASH        | Yes             | Electrical Erase | Nonvolatile | Yes      |

| Anti-Fuse    | No              |                  | Nonvolatile | Yes      |

| SRAM         | Yes             | Power Off        | Volatile    | No       |

Table 1.6

Technologies of PLD configuration cell

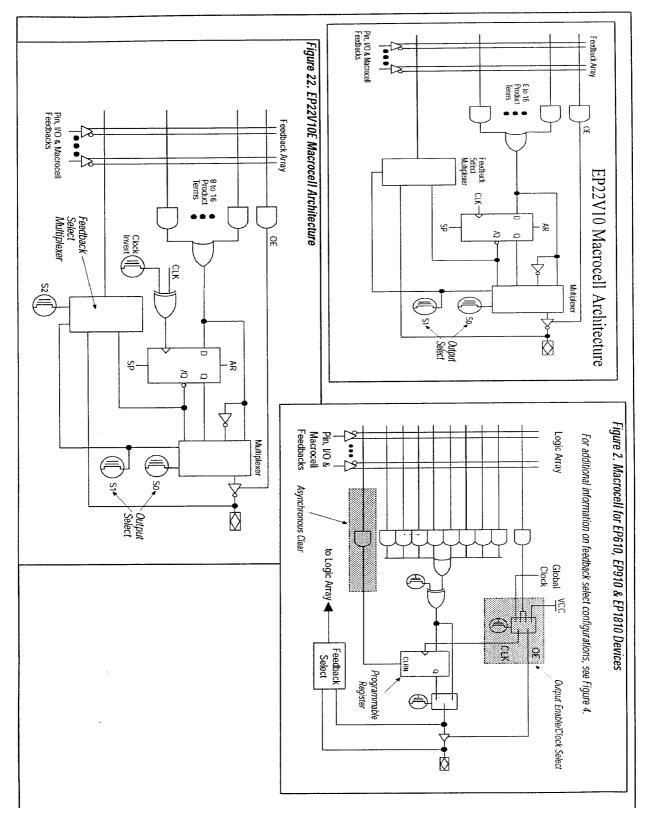

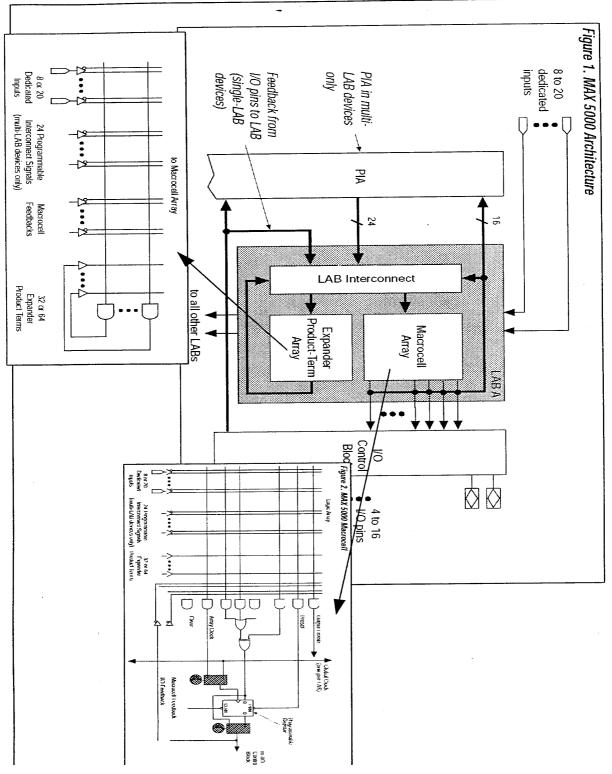

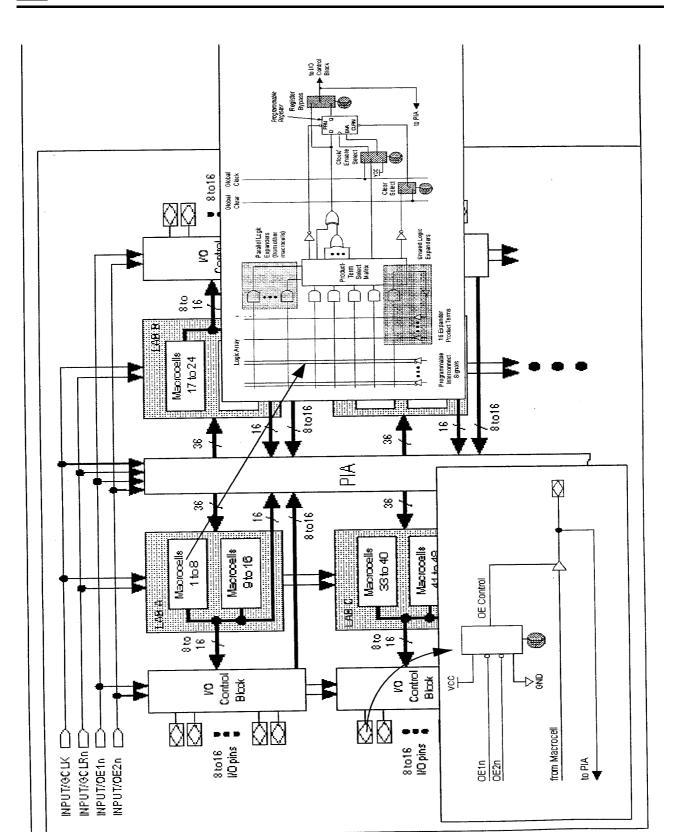

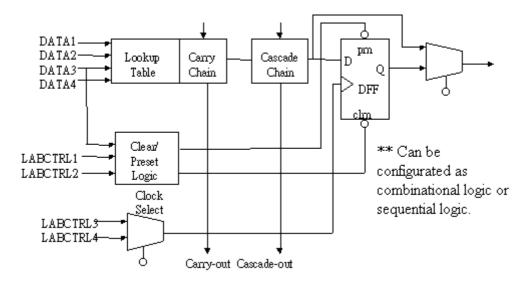

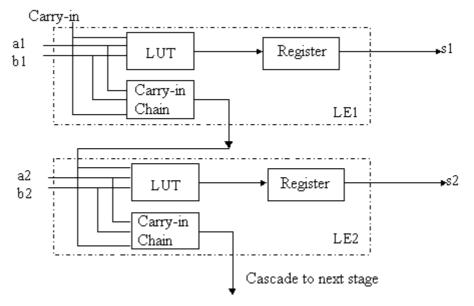

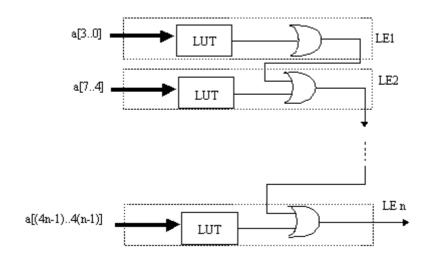

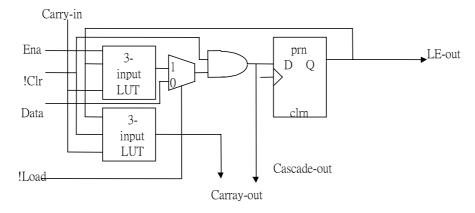

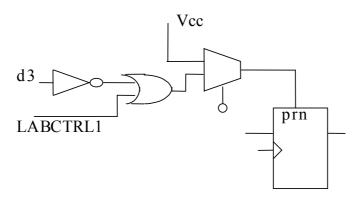

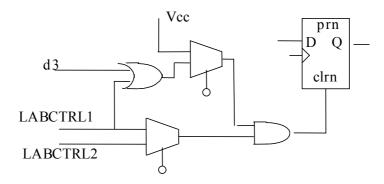

Logic cell has two main design trends. One is "Macrocell" with the structure of "sum of production term"; the other is "logic element" with the structure of "Look-up Table" (LUT). In Macrocell, all productions are summed up for exclusive-OR operation and then connected to a programmable flip-flop. Thus, Macrocell has greater logic capacity, and is only constrained by the number of productions (It also called "P-term".) A Marcocell usually has 20 to 40 logic gates. Logic element is usually made with 4 to 8 input LUT circuits, 1 or 2 programmable flip-flop, one faster carry circuit, and one sequentially-connected circuit to increase fan in (speed will not be affected a lot after sequentially connecting.). A logic element usually has 10 to 20 logic gates, and therefore a logic element is basically smaller than Marcocell. PLD with sum of production term has more logic gates, and so is very suitable for the circuits requiring more combination logic designs. On the other hand, PLD with logic elements is useful for the sequential logic circuits requiring more registers.

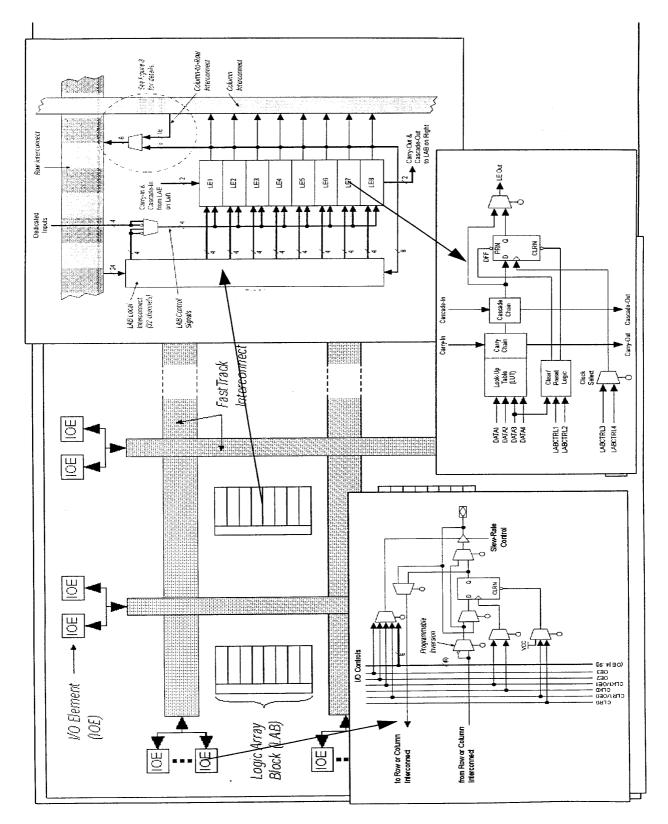

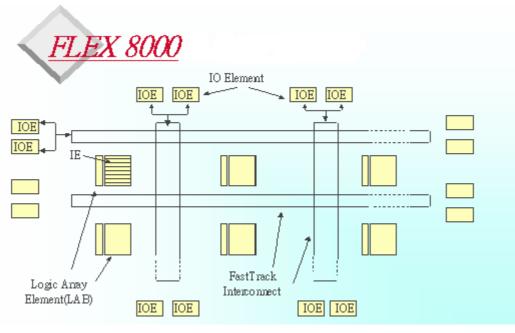

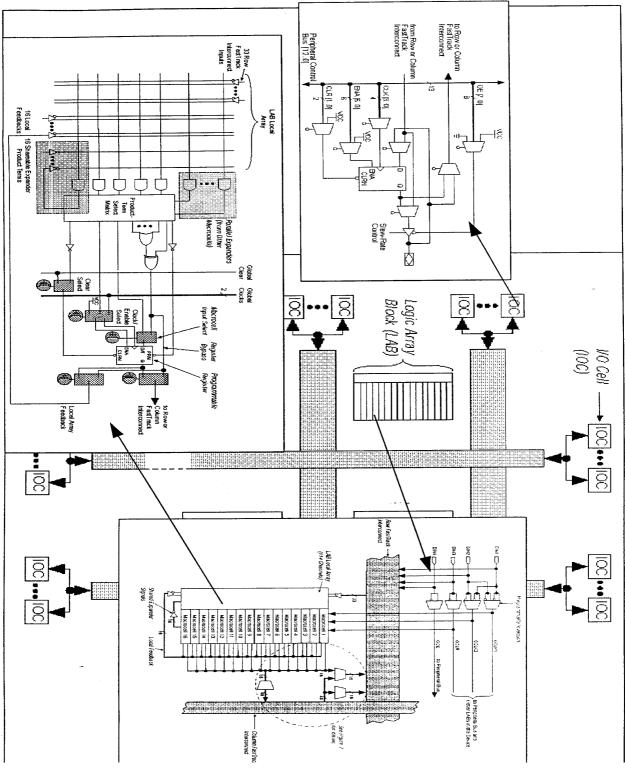

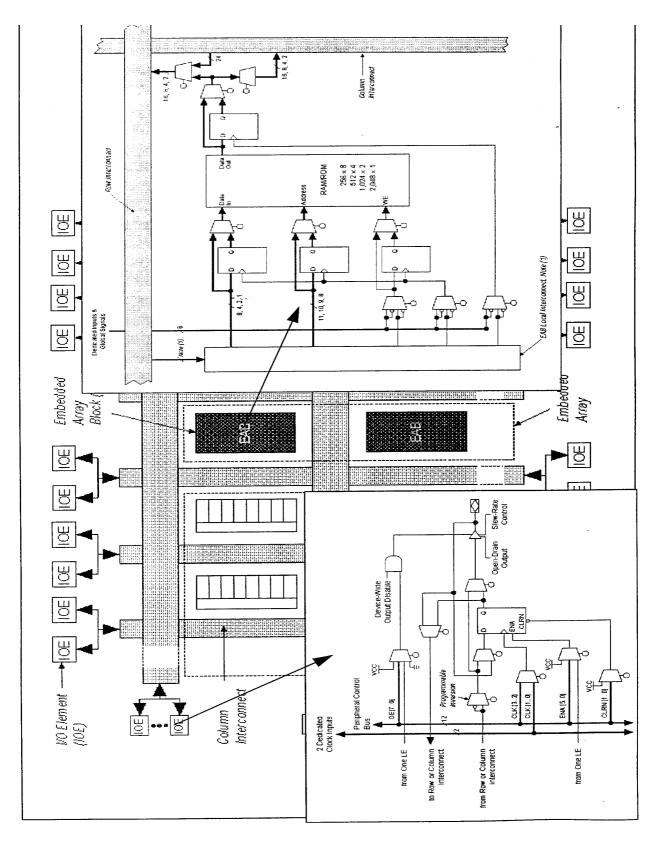

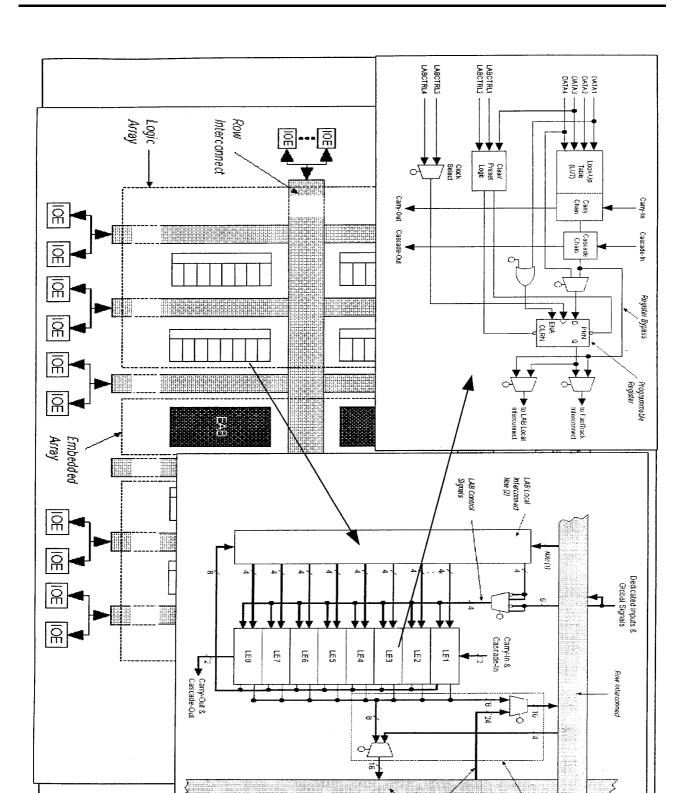

Interconnect structures give channels to deliver information from I/O ports to logic elements. Currently "FPGA segmented interconnect" and "CPLD continuous interconnect" are two mainly connection types, and this is the key difference between FPLD and CPLD interconnects structures. FPGA segmented interconnect uses varying length lines connected by pass transistor or anti-fuses to connect logic cells. Each connecting point has an on/off element to control connecting direction. To build up required interconnection, all signals will have to pass through cells by several long or short channels. Thus, whenever we modify a design, the routed path will be different and delay changes, and consequently, this segment connection cannot predict the time delay by interconnection. For continuous interconnection, it uses metal wires to round elements in horizontal and vertical directions. Each metal wire only can transfer one signal, and this is what we called "global" interconnection. Several (8 to 16) logic elements are collected in one Logic Area Block, LAB. Elements are connected to each other by local interconnection first and become LAB blocks, and then, LAB blocks are linked together to complete the whole connection by global interconnection. As a result of this interconnection, the delay is predictable.

To sum above, we have following conclusions:

- Because there is a complicated wiring job to decide, the time to translate FPGA is longer than CPLD.

- Because CPLD interconnection is simple, it quite reduces wiring spaces, and the number of gates can also be increased a lot by use of three-metal process.

- FPGA is helpful for data path application such as pipeline design. CPLD, comparably, is useful for logic applications.

ALTERA is a US company. It is specialized in PLD and sells all different PLD products, including PLD (Programmable Logic Device), PAL (Programmable Array Logic), PLA (Programmable Logic Array), GAL (General Array Logic), and FPGA (Field-Programmable Gate Arrays), etc., popular in the current market. In early age, an electronic engineer had to use breadboard and many logic elements to verify a new circuit design. Welding devices and correcting mistakes also made an engineer worn out. Contrarily, today an engineer can just use PLD and remodel the circuit designs in computer. It is just like making your own circuit devices on your own tables. It cannot just save welding time but also avoid any mistakes caused in welding process.

Moreover, it can reduce the PCB space to meet the market trends requiring smaller and lighter electronic products.

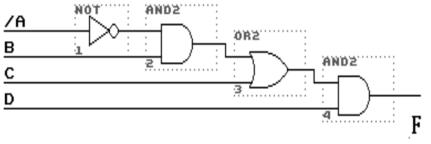

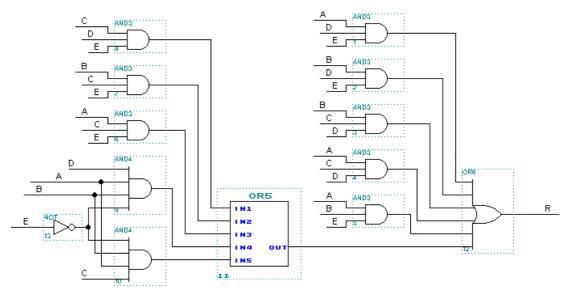

Because digital logic can be calculated by mathematics, we can use different circuits to achieve the same circuit functions shown as in Figure 1.5. Initially, an AND-OR can replace AND-OR-AND integrated circuit. We then assume we would like to make a simple structure which connections can be changed, as we need.

F=((/A&B)#C)&D

Figure 1.5 AND-OR-AND logic circuit

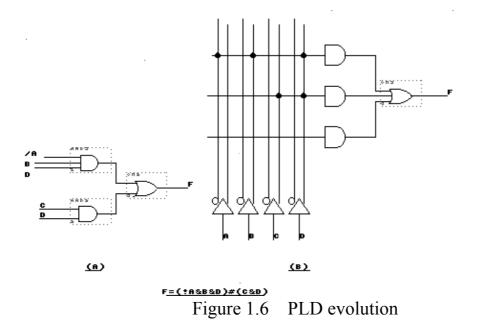

Similarly, the structure in Figure 1.6b is a simple single structure. It is made by several multi-input AND gates and OR gates. Each AND gate input uses the same input signals that can be connected to AND gate directly or inversely. However, not all input signals will be connected to AND gates. Users can decide if input signals

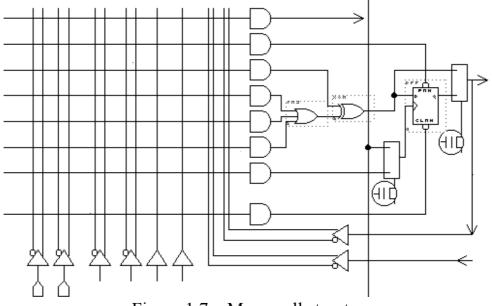

would be connected to AND gate. For example, if we have the logic function  $F = \{/A \& B \& D\} + \{C \& D\}$ , we can design a circuit as Figure 1.6b. If users have different circuit designs, they would also get different functions, and that is the first idea for programmable logic. For further explanation, we only have to extend the structure in Figure 1.6b, and logic functions will become more complicated consequently. This multi-input AND gates are called as P-term. For old PLD integrated circuit, it only has multiple P-terms like the structure in Figure 1.6b. Today, this kind of structure cannot meet most of engineers' demands. This is because of less gate counts and lack of Flip-flop. Therefore, in Figure 1.7, we add Latch and channel selection functions to the basic structure in Figure 1.6.

Until now, the general logic we have talked about is only a general structure. It requires users to decide which connection points they would like to link together and would not. Of course, referring to element structure, users can decide whether to make an interconnection for all circuit functions. For elements requiring less interconnection points, it might be acceptable. However, if elements have more than thousand interconnection points, this job would become very tedious and users would easily make mistakes. Thus, we need computer aids to help us to design circuits easily, and then use the software to make interconnection plan. Thereafter, we know a completed programmable logic world have to be done by programmable hardware and software to help design interconnection. For the two parts, we will discuss in the following section.

Figure 1.7 Macrocell structure

First, we would like to introduce ALTERA hardware. Usually PLD application is restricted by the hardware including inner gates and I/O pins. ALTERA produces gates from 150 to 1 million and pins from 20 pins to 560 pins for its devices. Definitely, those numbers are still being updated, and we know ALTERA can give users broad and various selections. Beside that, interconnection is also one of ALTERA's unique features. Because ALTERA uses metal wires for its interconnections, and it adds extra metal wire connection between any two Logic Blocks. We call this connections as "continuous interconnect", different from "segmented interconnect". Because of this difference, its interconnection time delay is predictable and would not be affected by interconnection path.

# **1.3.1 ALTERA CPLD:**

Until 2000, ALTERA devices can be divided into 10 different families:

- 1. CLASSIC

- 2. MAX3000

- 3. MAX5000

- 4. MAX7000

- 5. FLASH LOGIC

- 6. FLEX6000

- 7. FLEX8000

- 8. MAX9000

- 9. FLEX10K

- 10. FLEX20K

MAX7000 family has members: MAX7000, MAX7000E, MAX7000S, MAX7000A and MAX7000AE, etc. FLEX10K family has members: FLEX10K, FLEX10KA, FLEX10KB, and FLEX10KE, etc.

In the programmable logic world, the unique feature is a logic cell can be reproduced continuously in a chip. The difference between higher capacity and lower capacity of

devices in the same family is the amount of the reproduced logic cells. Therefore, we could understand other devices from the smallest device in the same family.

Other relevant information, please see Appendix A and B.

# **1.4 PC Aided Digital Logic Design**

In previous section, we have briefly talked about ALTERA devices, and know ALTERA has all family devices. However, we still have many questions need for solutions. As a device has a lot of interconnection points, if users have to make connected-or-disconnected decisions for all points, it will obviously increase the difficulties to the job. Thus, a good PLD must have great design software to help users complete the work effectively and efficiently, and so ALTERA is currently more focusing on software development while designing great family devices.

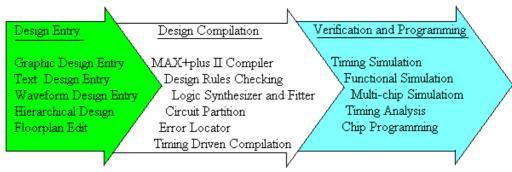

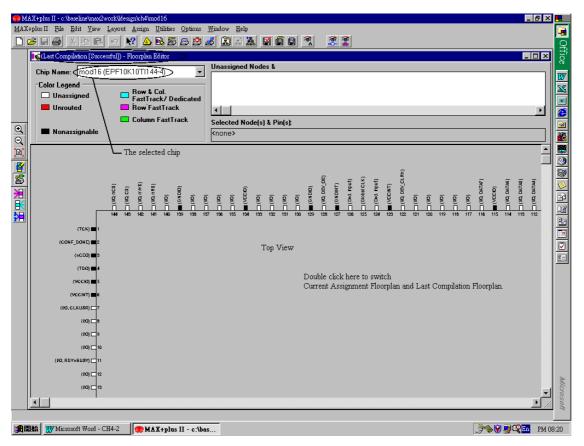

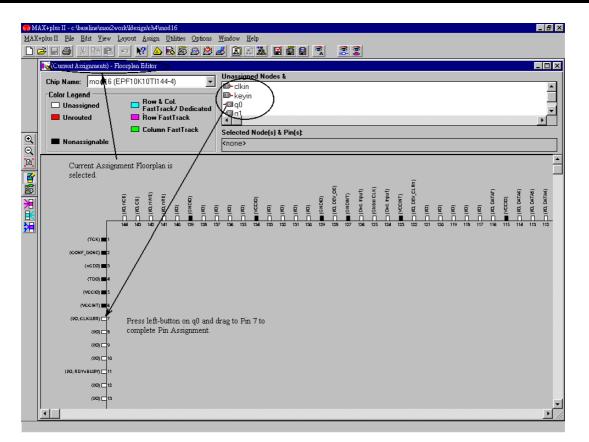

PLD Computer Aid Digital Circuit Design means engineers could use computers to complete PLD digital circuit design. This is a new design environment. It offers an integrated data management, hierarchical design, and multi-window environment. The design process includes four steps: design entry, compilation process, verification simulation, and PLD programming. The first step is "design entry". It includes graphic editor, text editor, and waveform editor. A hierarchical mix entry, which is a combination with graph, text, and waveform, is the best way of design.

Compilation is the process including the testing of electric feature of entry circuits (e.g. short cut and source less input, etc.), circuit synthesize and netlist extract for functional simulations, circuit floorplan (that is to fit the circuit into PLD), and the netlist extract for timing simulation as well as the creation of PLD programming files. Verification simulation can be divided into functional simulation and timing simulation. Functional simulation is actually timing simulation when we assume propagation delay and setup time is zero. Timing simulation, on the other hand, is the simulation performing based on the value of the propagation delay and setup time from actual circuit floorplan into real PLD. Functional simulation could roughly verify circuits first to ensure circuit functions meet specifications. Timing simulations then further ensure the circuits work well in PLD.

Then after verification, programming PLD is a must process. There are two technologies: (1) download with SRAM technologies; (2) programming with EPROM, EEPROM, and FLASH are adopted in PLD. The download technology is useful during R&D and learning periods; programming, however, is very helpful when circuits are well developed already or circuits would not be modified in a short time. No matter which technologies we would use, it needs to have development tools to complete the work effectively and efficiently.

From a design diagram, the PLD Computer Aid Digital Circuit Design System is the great tool for engineers or students to complete their work efficiently. Because the systems can offer great circuit entries, verification simulation, devices programming environments as well as integrated data management, they shorten the time to design new circuits and catch up the time to market efficiently. Besides the above basic functions, PLD Computer Aid Digital Circuit Design System also has the following features:

1. Hierarchical design with mixed entries: Graphic editor is quite useful for a small logic design. Because the transformation can easily completed from Truth table or state diagram to logic gates by workforce. Logic gates are then entered into the form of graphic editor. However, it will become very time consuming and easy to make mistakes to complete the transformation by workforce when trying to make a big logic design. Therefore, like writing any programs in C language, we use texts to describe circuits and have computers, which specialize in computing and mapping algorithms to handle the transformation, making circuit modification easy. Moreover, a circuit has hundred thousand of gates, which have great duplication, and graphic entry becomes a hard and complicated task. No matter in terms of design or fault detection, graphic entry is more difficult than text. Beside graphic and text entries, we could also use waveform entry to describe circuits. By wave entry, we could know the output that input data would be related to, if we assume the circuits as a dark box. The computers are asked for the generation of Truth table or state diagram. Thus, the generated circuits might not be the simplest ones. The three entries have their own benefits

and drawbacks. They are all useful in different areas. If we use the three together, we could further improve efficiency in design and affectivity in teamwork. To combine the three together, hierarchical design function, therefore, is essential.

- 2.Structure independent: During the early stages of design entry, functional compilation (including logic synthesis and minimization as well as netlist extract for simulation), and functional simulation, engineers do not have to concern which PLD device will be used and what the internal structure is. This is what we called "Structure Independent". Until the end of design compilation, by technology mapping algorithms, we then place synthesized circuit on the selected PLD. If the circuits are too big to be fitted in a piece of device, we might partition the circuits before placement or change a bigger device. This unique feature gives a great flexibility for future use of PLD.

- 3.Providing industry-standard LPM: LPM element is a macro-function, which allows users to change its sizes based on parameters. For example, the length of LPM counters and LPM adders is a parameter that can be changeable; the type and the number of bits of LPM multiplexer and LPM register are another changeable parameters. The LPM provides a simplified design entry and has better circuit integration.

- 4.Providing time driven compilation: To increase performance of the designed circuits is the goal for engineers in the second stage, or to meet the propagation delay  $(t_{pd})$  and the speed  $(f_{max})$  are defined on the deign specification. If a development system could provide time driven compilation, it could reduce much complicated work based on the user specification to synthesize circuit integrate and plan as well as allocate circuits.

- 5.Providing multi-device simulation function: When designing big circuits, we usually partition circuit into several smaller PLD devices. At this moment, a singular-device simulation might have some problems and cannot fully and efficiently assist engineers to complete their whole design projects. Therefore, it would be better to have multi-device simulation functions to make design process more smoothly, easily, and correctly.

- 6.Great Design-rule checking ability: In design process, if development systems could early find some unreliable logic problems such as static hazards, race condition, multi-level clocks and asynchronous input, etc., we could greatly decrease circuit failures. Therefore, this feature can much shorten the leading time to launch new circuits in the market.

- 7.Providing standard CAE interface: To connect with other EDA design systems, we should systems that have interfaces able to read and write VHDL and EDIF. Because of the interface to connect with other systems, we could share design resources and conveniently and efficiently complete the design projects with our team members.

In the next section, we will detail the EDA tool of ALTERA-- MAX+PLUS II.

# **1.4.1 ALTERA EDA Tool-MAX+PLUS II**

ALTERA EDA tool is a kind of software called "MAX+PLUS II". Until 2000, it already has version 9.x. This software can support designers from design entry to the creation of programming file that programs interconnection as well as simulation process. In another words, designers can use the same software to complete all design process. There is no need to get another software from third party to support ALTERA hardware devices. Once designers familiar with MAX+PLUS II, all logic design can be totally completed by this same software. In this case, designers or students do not have to continuously learn different software and therefore save more time. When designers need same-function logic circuit, they do not have to repeat the design process again and only have to save the circuit as an element in MAX+PLUS II firmware library. By calling the element, designers can add the circuit into their designs, and interconnect each of element inputs and outputs to reduce lots of work for logic design entry.

Figure 1.8 MAX + PLUS II functional diagram and design flow

MAX+PLUS II is a window application tool. It ca be used with Windows 95/98 and Windows NT. At the same time, ALTERA also offers a workstation edition. Therefore, the use of MAX+PLUS II is the same as the use of general window applications. Mostly it operates with graphs. Figure 1.8 indicates MAX+ PLUS II functional diagram and design flow. Fundamentally, a programmable logic design has 3 major steps:

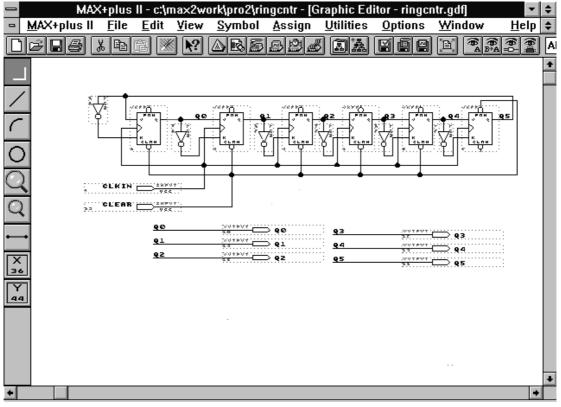

Design entry: In previous section, we already know workforce cannot program all interconnection points efficiently, and it will become more difficult for a bigger circuit design. Thus, we need a user-friendly tool to describe the logic circuit that we want. It is just like programming. Designers can use C language to write programs. They can also use assembly or even machine codes to write programs. It is easy to understand the advantages and disadvantages of design entry by using C language. Figure 1.9 indicates the graphic entry in MAX+PLUS II.

**Design compilation**: After design entry, incorrect description or electric faults can be detected by compilation. Once all circuits are correct, compilers will follow designers' direction to synthesize circuits into selected devices (that is logic synthesis and floorplan.), and generate programming files for programming devices.

**Verification and programming**: After completing above two steps, we already have a programmed device. However, there might still have some problems. For example, design description is accurate but circuit function is incorrect. In another words, it is because design is incorrect (logic error) or devices cannot meet the real requirements (timing error). Therefore, it is still necessary to use real circuits to verify the devices and ensure they are applicable in the real world. Simulation, as a result, could identify circuit operation status without physical circuits. It greatly helps designers to detect faulty problems in early design process.

Figure 1.9 Graphic entry in MAX+PLUS II

The following is MAX + PLUS II functional description:

Design entry : Fundamentally, MAX+PLUS II has three ways to input designs. Those

three can be used together in one circuit design; that is, they can mutually use together. Designers can choose the best ways to make each partial circuit as "sub-circuit" separately, and combine all of them together finally. In MAX+PLUS II, it also has had standardized 74 family functional elements. Designers can call the elements out and use them directly. MAX+PLUS II software also provides the features of Library of Parameterized Modules (LPM). Designers only need to set up LPM parameters in advance. Various functional circuits will be generated automatically with different bits and functions. For example, memory, adder, and multiplier are parameterized.

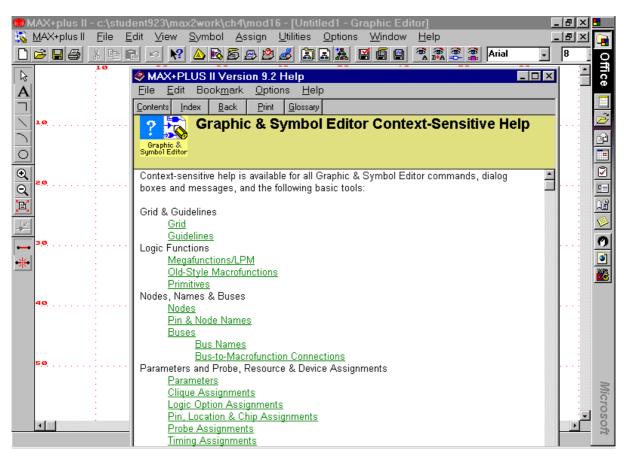

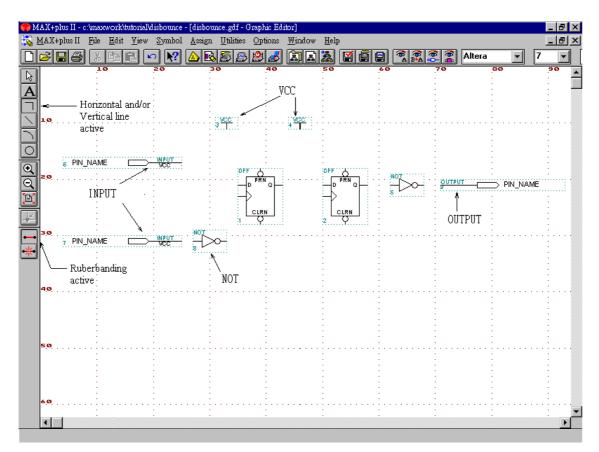

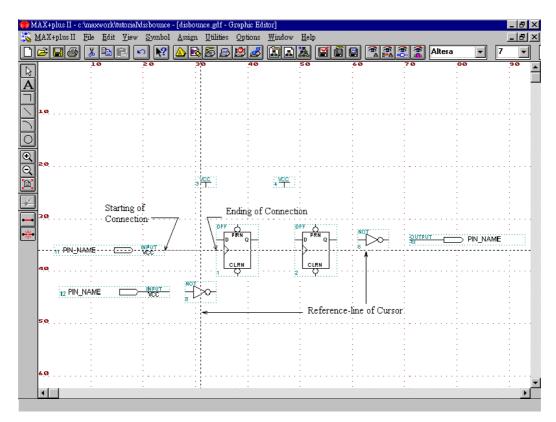

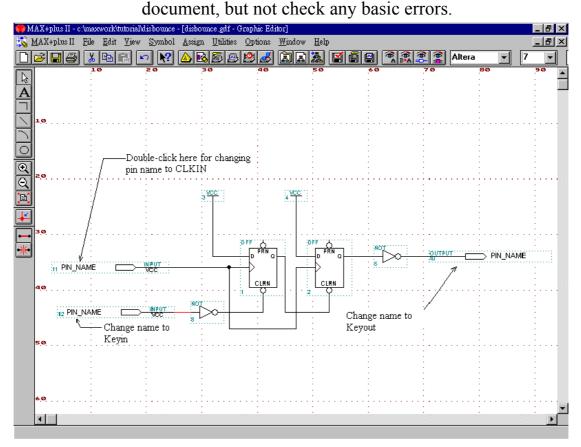

- **Graphic entry**: Graphic entry is the most acceptable technology by designers. To complete design entry, it only requires interconnection between functional blocks, like drawing circuit diagrams. Figure 1.9 is Graphic entry in MAX+PLUS II.

- **Text entry**: Though it is easy to design circuits by graphic entry, it pre-requires all designs completely first, including Truth-value table or state diagram needed to be reformed into logic circuits by workforce, and then entered in graphs. However, once a design fault is found and needs to be corrected, we have to redo all calculation and design entry. Contrarily, if by text editors, we only have to correct the design fault, not to redo the whole process, and then have computers to handle all the calculation, and that is computers' expertise. For sure, this is just one of text entry benefits. Not like graphic entry, text entry does not have hundreds or thousands of graphs needed to enter. It makes the jobs easier on circuit design and error detection for devices with thousand gates. MAX+PLUS II totally have three description languages: ALTERA Hardware Description Language, VHDL, and Verilog HDL. Figure 1.10 is Text entry in MAX+PLUS II.

112

|                               |            |                                      | 017       |               | C 19 7               |     |                |

|-------------------------------|------------|--------------------------------------|-----------|---------------|----------------------|-----|----------------|

|                               |            | \max2work\pro<br>t <u>T</u> emplates |           |               |                      |     |                |

|                               |            |                                      |           |               |                      |     | Help 🛊         |

|                               | <u>в</u> Ē |                                      | <u>SB</u> | <u>9</u> # [1 | à Me                 | BBĨ | <b>*</b> * * * |

| TITLE "SEVEN<br>SUBDESIGN 7SE |            | BCD CODE DE                          | CODE";    |               |                      |     | +              |

| (                             |            |                                      |           |               |                      |     |                |

| DATAIN[3.<br>DISPLAY[6        | .0]        |                                      |           |               | : INPUT;<br>:OUTPUT; |     |                |

| )                             | 0]         |                                      |           |               | :001F01;             |     |                |

| BEGIN<br>TABLE                |            |                                      |           |               |                      |     |                |

| DATAIN[]                      |            | DISPLAY[60                           | ];        |               |                      |     |                |

| 0                             |            | B"1000000";<br>B"1111001":           |           |               |                      |     |                |

| 2<br>3                        | = >        | B"0100100";                          |           |               |                      |     |                |

| 3                             |            | B"0110000";<br>B"0011001":           |           |               |                      |     |                |

| 4<br>5<br>6<br>7              | = >        | B"0010010";                          |           |               |                      |     |                |

| 6                             |            | B"0000010";<br>B"1111000";           |           |               |                      |     |                |

| 8                             | = >        | B"0000000";                          |           |               |                      |     |                |

| 9<br>END TABLE:               | = >        | B"0010000";                          |           |               |                      |     |                |

| END;                          |            |                                      |           |               |                      |     |                |

|                               |            |                                      |           |               |                      |     |                |

|                               |            |                                      |           |               |                      |     |                |

|                               |            |                                      |           |               |                      |     |                |

|                               |            |                                      |           |               |                      |     |                |

|                               |            |                                      |           |               |                      |     |                |

| Line 1 Col                    | 1          | INS +                                |           |               |                      |     | +              |

|                               |            |                                      |           |               |                      |     |                |

Figure 1.10 Text entry in MAX+PLUS II

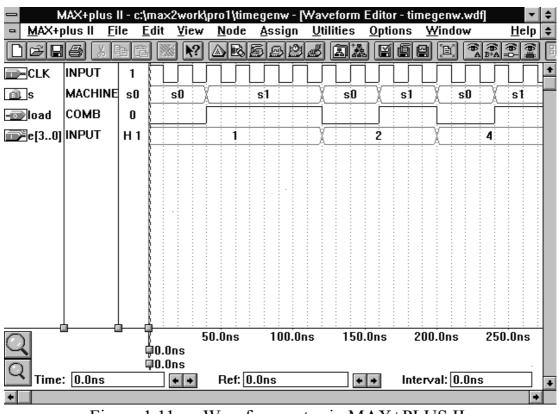

- **Waveform entry**: Waveform is the third way of MAX+PLUS II design entries. It allows users to describe circuit functions by drawing waveform directly. Figure 1.11 is Waveform entry in MAX+PLUS II.

- **Industry-standard CAE entry**: EDIF is an industry-standard CAE netlist file. MAX+PLUS II uses this standard file format to communicate with other CAD software such as Synopsis, Viewlogic, Cadence, and Mentor Graphics, etc. It also offers functional library for them. Currently, MAX+PLUS II has two standards. One is EDIF200 and the other is EDIF300.

Figure 1.11 Waveform entry in MAX+PLUS II

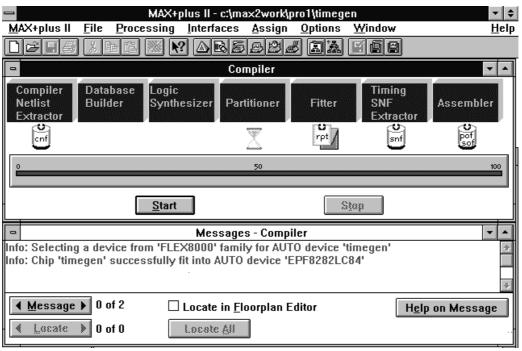

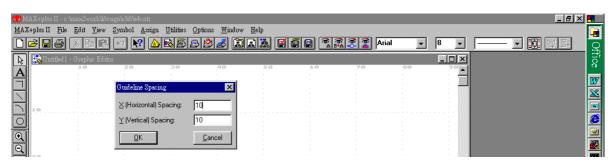

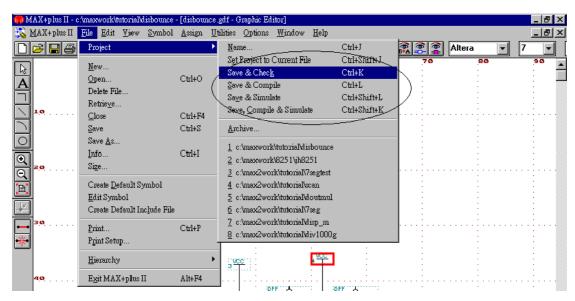

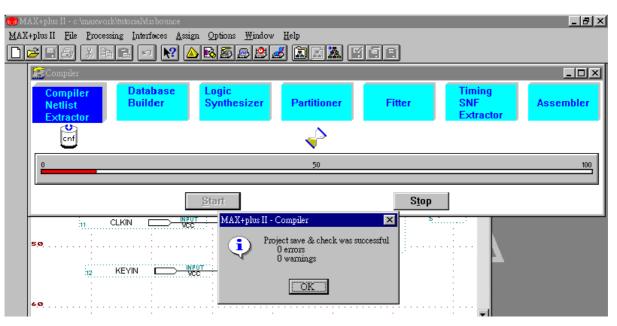

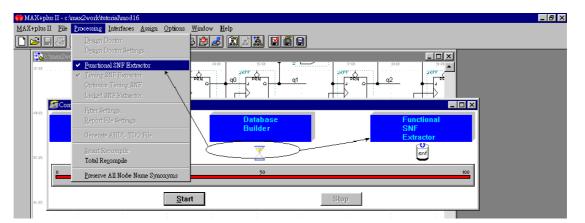

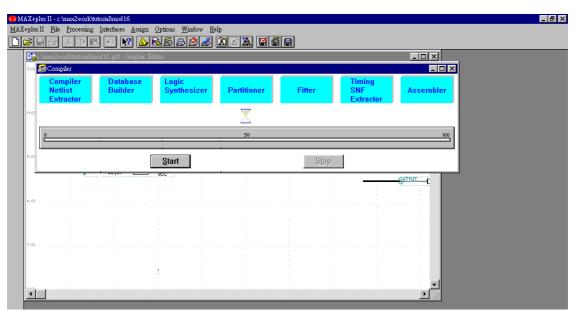

Design compilation: No matter what design technologies and ALTERA devices are adopted, to complete logic synthesis after verifying a circuit's electric features, it is necessary to pass compilation process shown in Figure 1.12. Once compilation is finished, we will get programming files and some information such as the reports of delay status and pin count arrangement. During this process, it also provides some convenient tools to help designers find faults and increase efficiency. The functions of compilation are described as below:

- (1) Design-rules checking: In the early of compilation, it can detect potential problems from design files, such as oscillation and pointing out location as a reference for designers.

- (2) Logic synthesis and fitting: This is the core part of the whole software. It can give you logic synthesis and circuit fitting based on the PLD structures you choose. After giving synthesis and fitting, it then decides all interconnection for the whole circuit design.

- (3) Multi-device partitioning: If a design file cannot be fitted in a certain selected device, software will automatically divide the design file into two more devices. This process could be fully or partially done by workforce. It

allows us not really separate design files, and only has to reset data for future use.

- (4) Timing-driven compilation: This function allows users to set up some timing parameters such as delayed time and highest frequency, etc. A compiler will follow the parameter setting and try to come out desired solutions on its best. However, because of the structures of logic elements, designers can take advantages of time-driven compilation only when adopting the devices of FLEX8000 and FLEX10K families. If adopting other family devices, it is not necessary to have this kind of function.

- (5) Automatic error location: During compilation process, whenever a design fault is found, systems will show an error message. By using automatic error location features, the systems will automatically open the files that have errors occurred, and then indicate the error locations clearly.

Figure 1.12 Design compilation in MAX+PLUS II

#### Verification and programming:

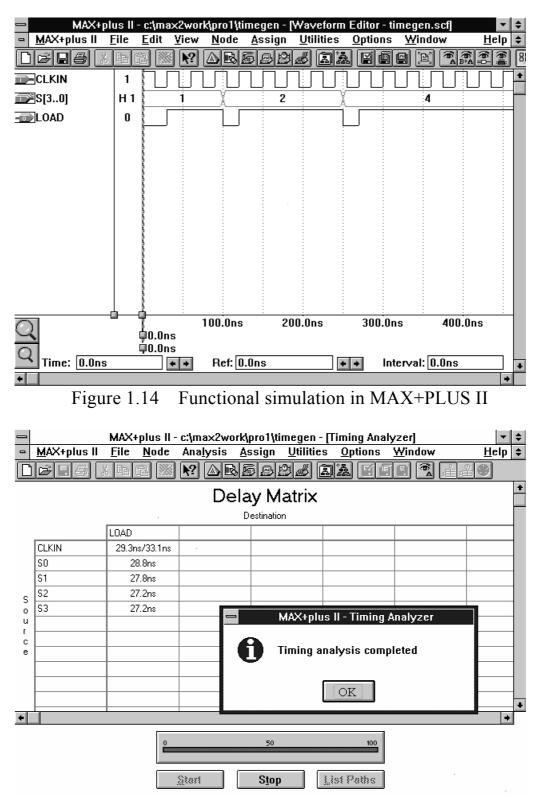

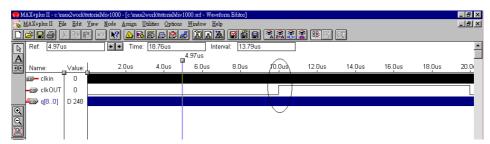

Simulation: Designers can use waveform editor to define the input waveform of the designed circuits. After entering waveforms, the software can automatically simulate and display output waveforms for inspecting design. In MAX+PLUS II, there are three simulations: 1.) Timing simulation including delay time and setup time of devices selected by designers, 2.) Functional simulation excluding delay time and setup time of devices selected by designers, and 3.) Multi-device simulation allowing users interconnect several ALTERA devices and then simulate all together.

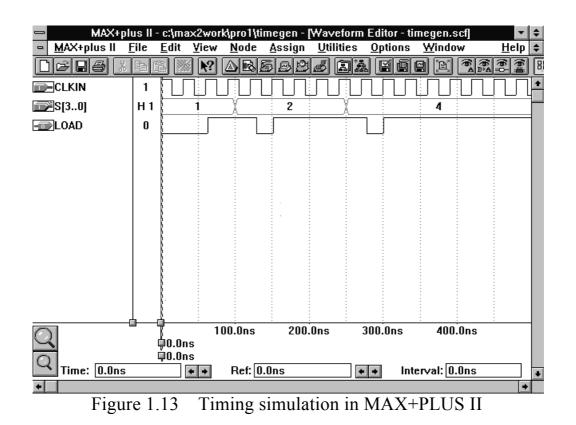

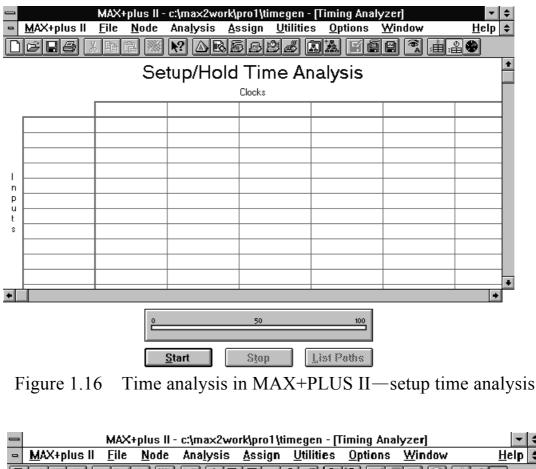

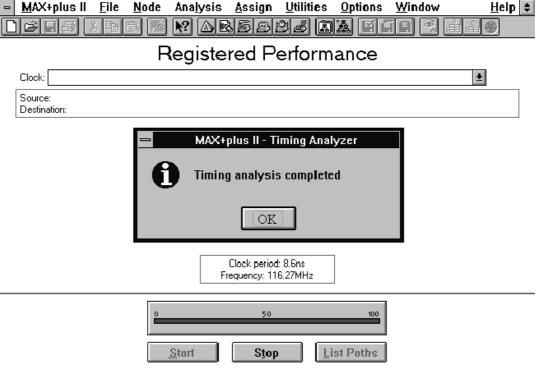

(2) Timing analysis: This function helps designers to understand timing performance by numbers at the beginning of design projects. The timing performance, for example, is as delay time, setup time, and registered performance analysis shown in Figure 1.13 to 1.17.

Figure 1.15 Time analysis in MAX+PLUS II—delay time analysis

Figure 1.17 Time analysis in MAX+PLUS II—registered performance analysis

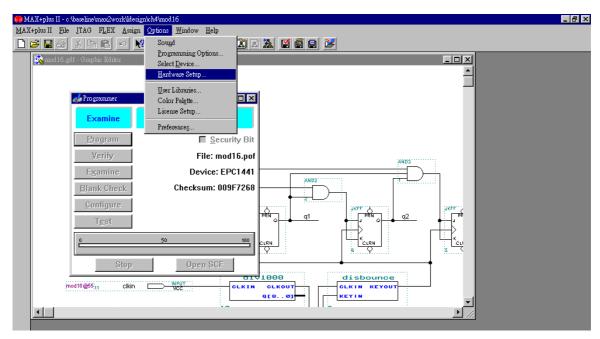

(3) Device programming: When software completes all process, configuration data will be programmed or written into relative devices for testing hardware.

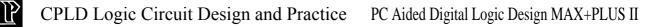

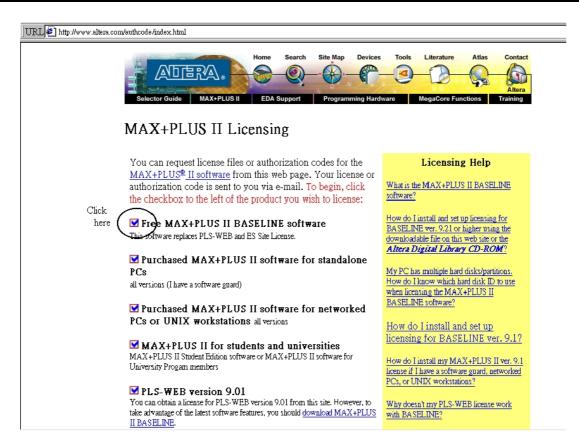

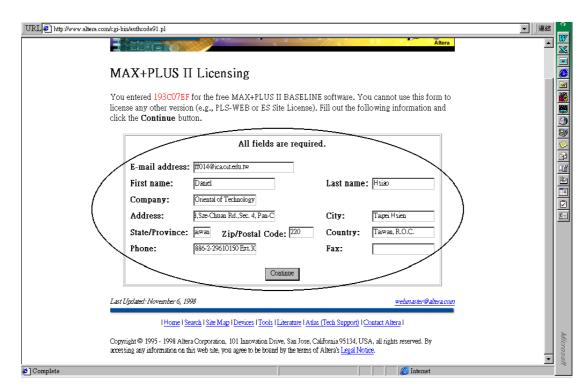

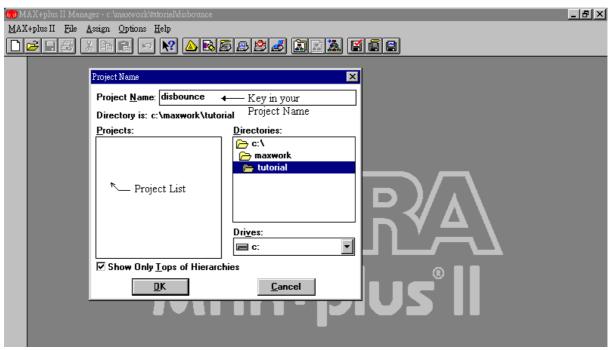

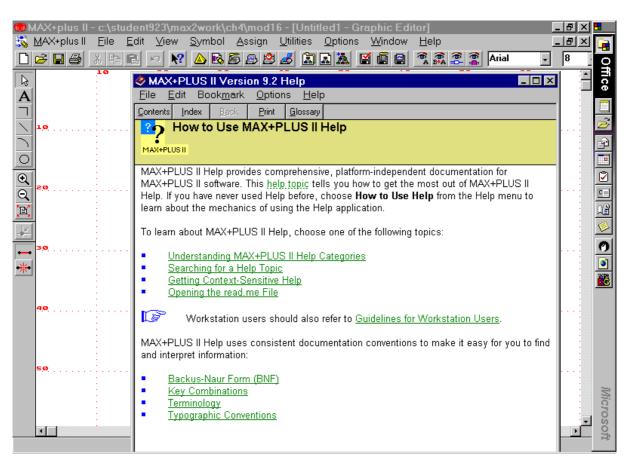

The above is the introduction of ALTERA devices and software. Currently, ALTERA provides free software of MAX+PLUS II for users with registration requirement. The operation process of the free software is the same as commercial version but only available for the devices of the families of CLASSIC, MAX5000, EPM7032, EPM7064, and EPM7096 as well as EPF8282. Meanwhile, it does not support waveform entry, and multi-device partitioning and simulation, etc. Other than that, the rest of the functions are exactly the same as MAX+PLUS II commercial version. About the user guide, MAX+PLUS II has great on-line help. We will further discuss how to set up and use the software of MAX+PLUS II Baseline 9.23 in Chapter 4.

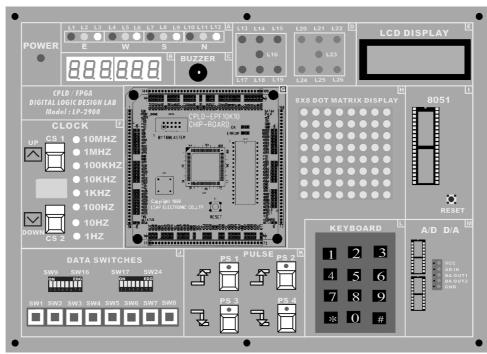

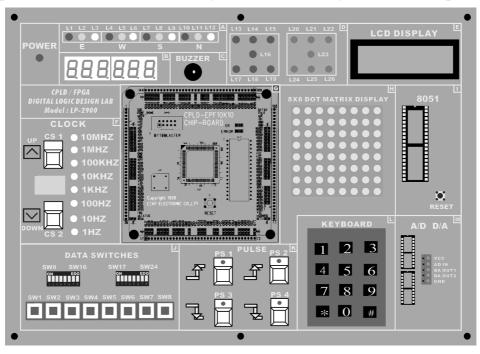

## **1.5 Experimental Platform**

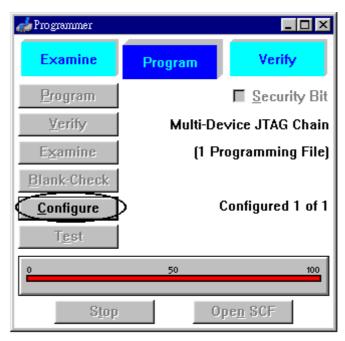

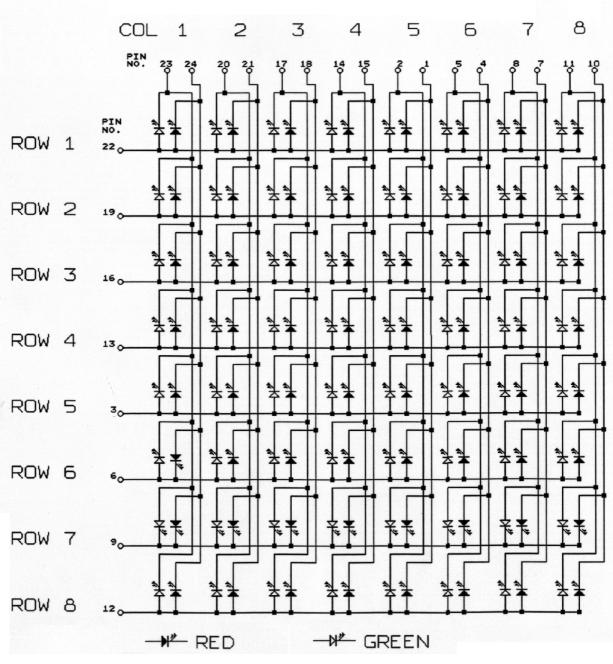

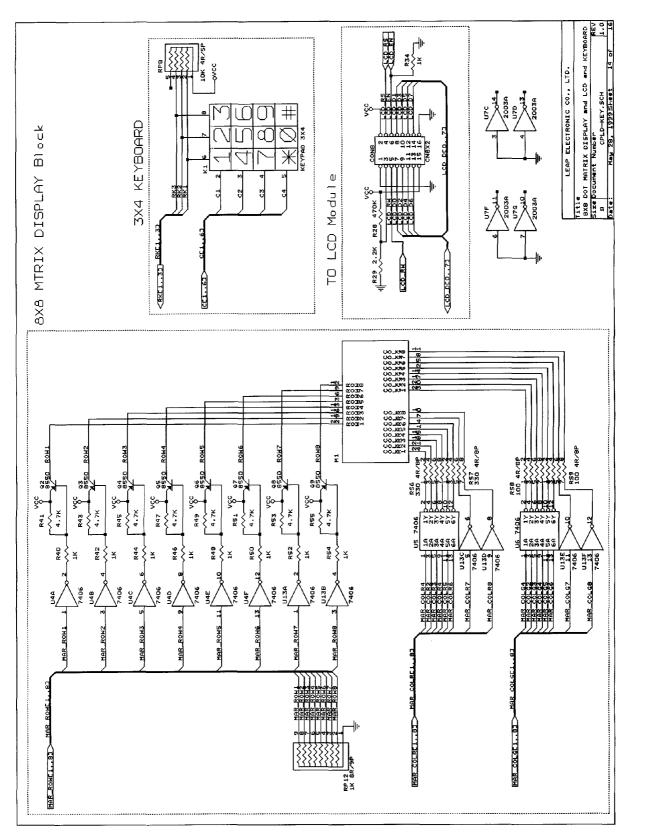

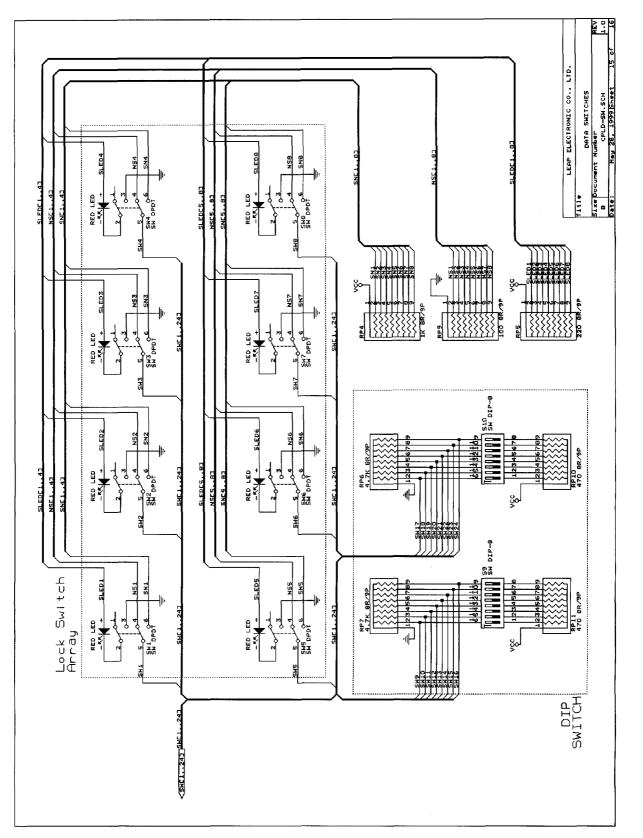

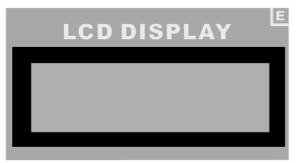

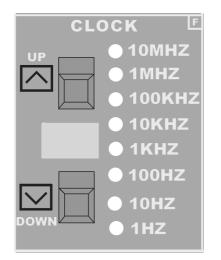

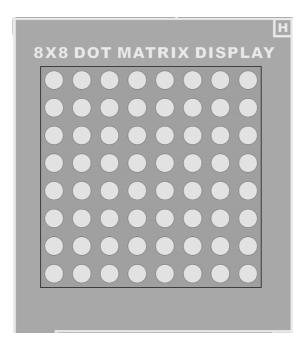

An experimental platform is essential in the integrated digital logic design environment. It not just requires SRAM CPLD device, but also power, downloading interface, and I/O elements which include LED, seven segments display, buzzer, clocks, switches, pulse switches, 43 keyboard, 8×8 dot matrix display, liquid display, and A/D & D/A circuit modules. The main purpose of the platform is to offer a simple and accessible environment to test circuits and to reduce the time needed for circuit design.

## 1.5.1 LP-2900 CPLD Logic Design

## **Experimental Platform**

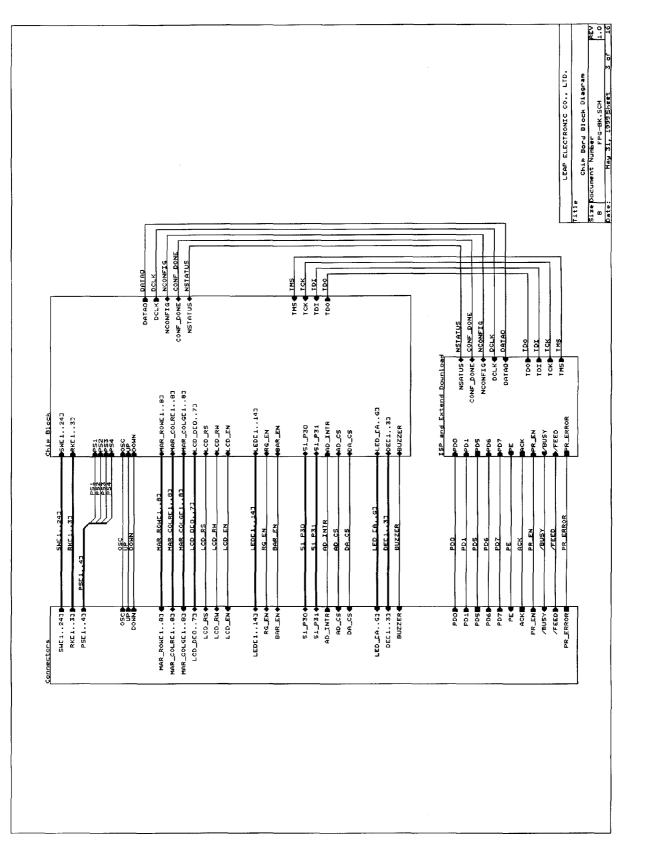

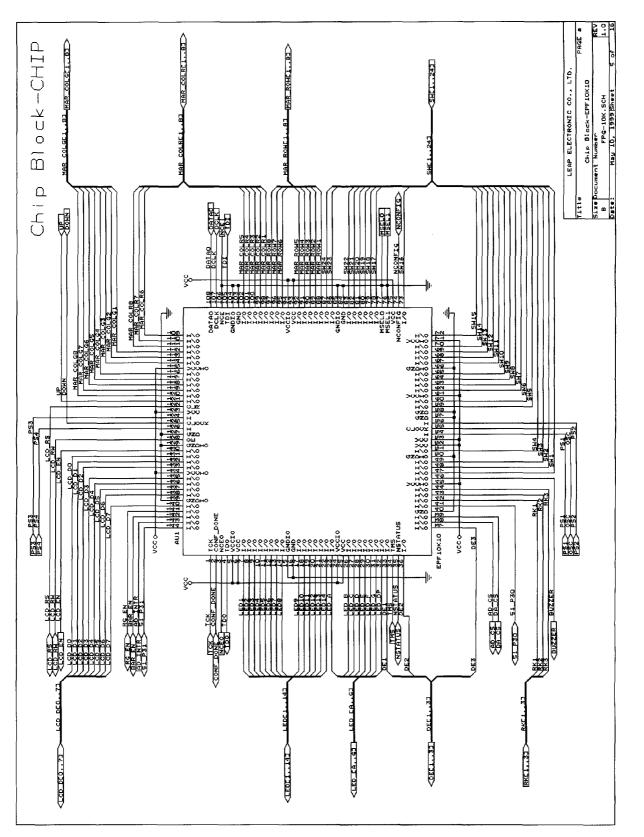

In Figure 1.18, LP-2900 CPLD logic design experimental platform was the new product of Leap Company in 1999. The company currently focuses on the development of the logic experimental platform, which has the learning environment that integrates design, simulation, and verification. The development also has the educational features such as easy setup, great access, quick response, and progressive

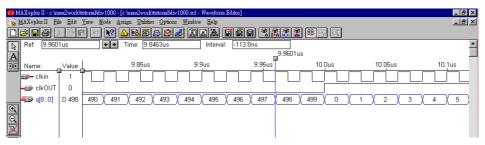

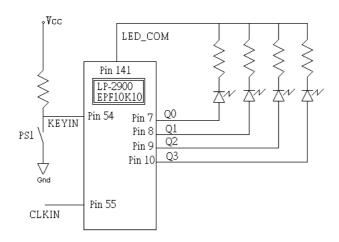

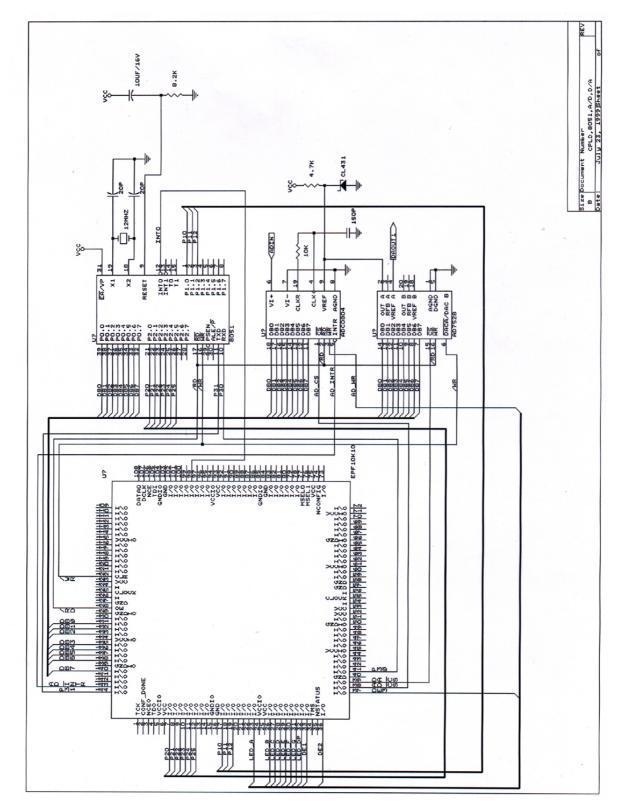

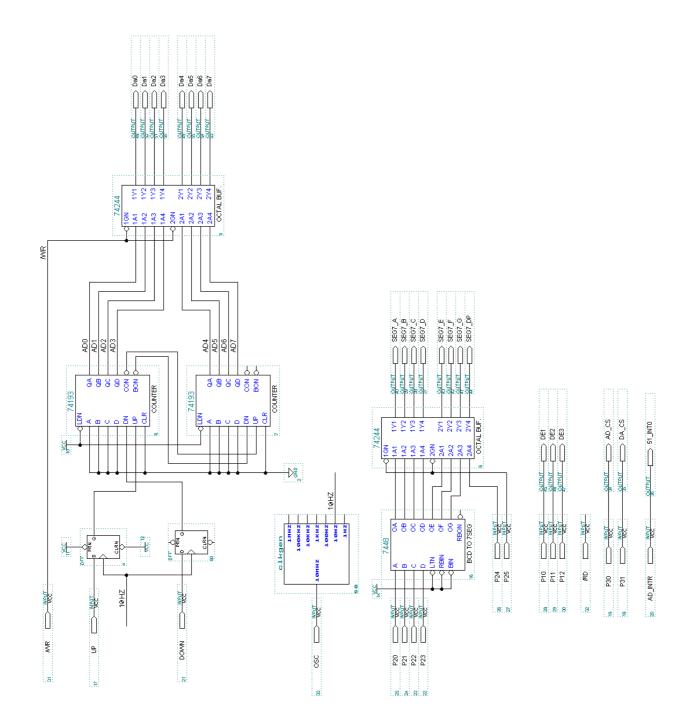

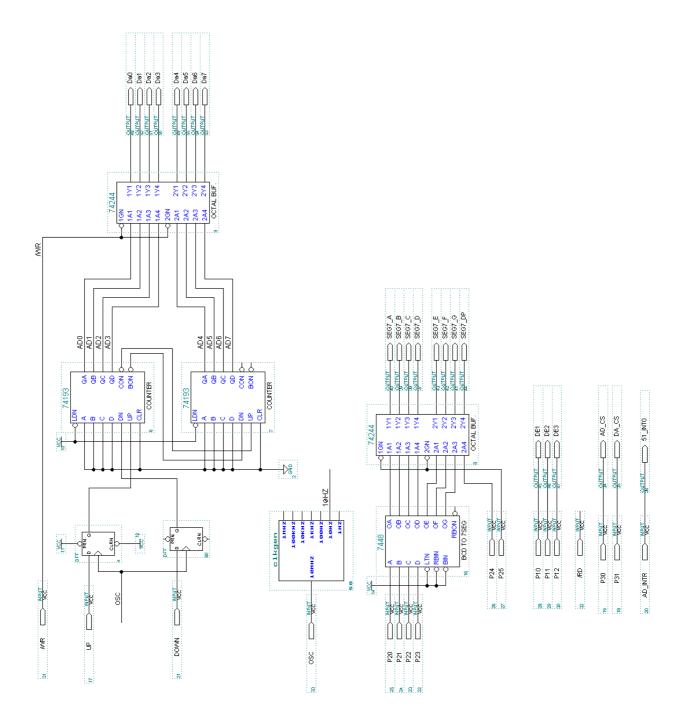

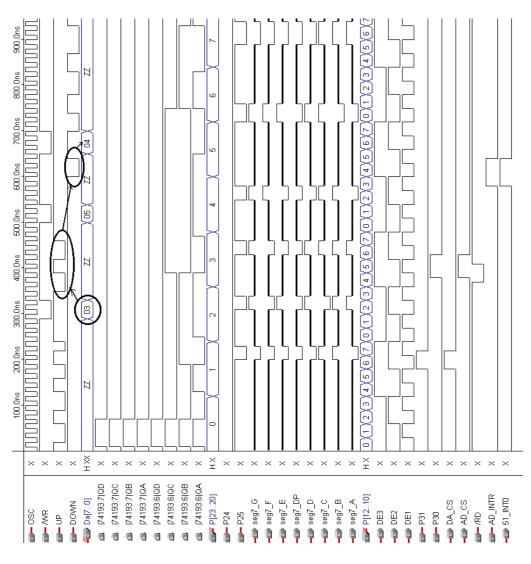

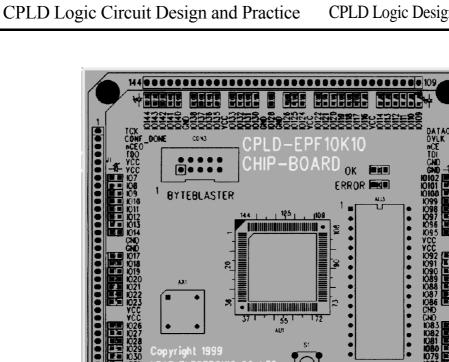

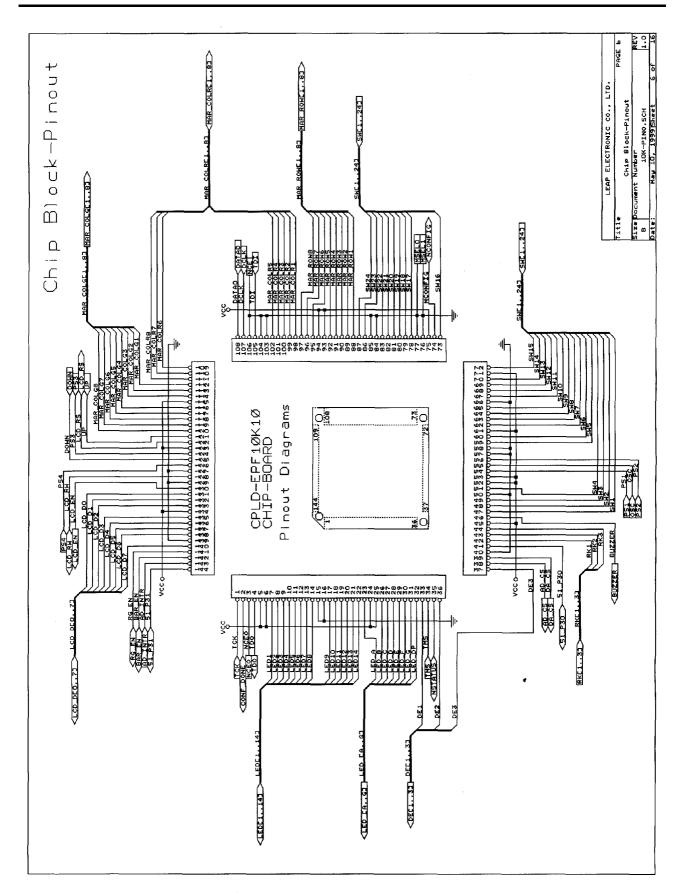

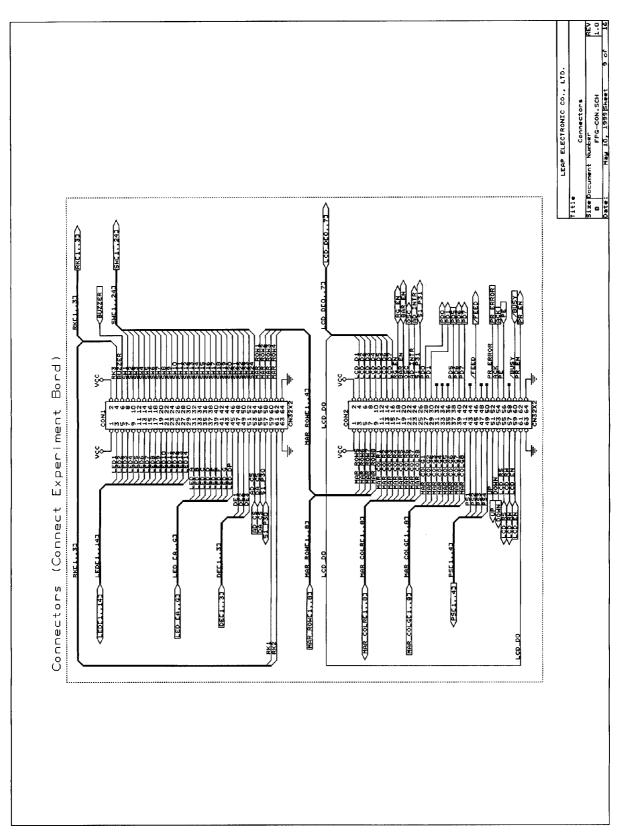

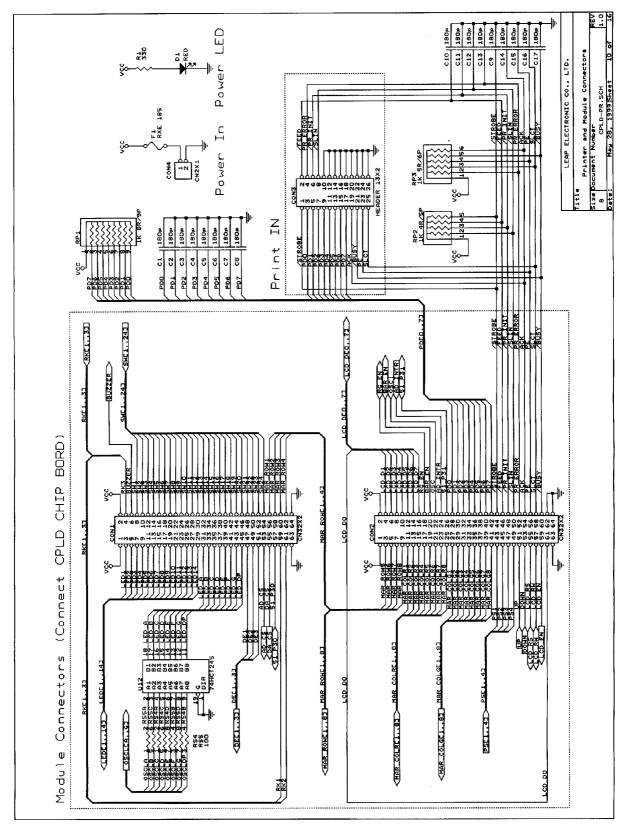

learning. It is based on ALTERA EPF10K10TC144-4 CPLD to develop a multi-function logic design experimental platform. The platform has CPLD device board, I/O element experimental board, PC download interface, and power.

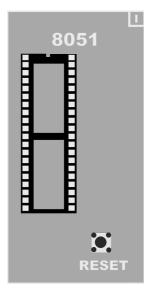

#### CPLD

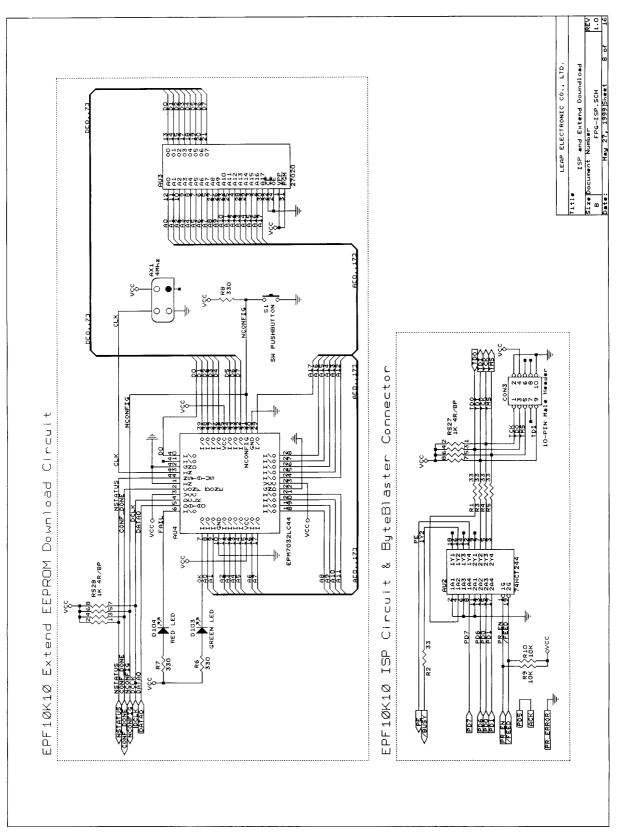

On the CPLD device board, there are an ALTERA 10K device, an EPROM device socket, a reset switch, and a pin status display LED which is a surface mounted device (SMD). ALTERA EPF10K10TC144-4 CPLD devices provide flexibility and convenience for continuously downloading and programming new circuits. The sockets of EPROM devices can be plugged EPROM devices programmed with "configuration data", providing another way to program EPF10K10TC144-4 CPLD devices. A reset switch changes 10K devices from user mode to command mode. After circuit configuration and circuit reset, 10K devices would back to original user mode. A pin status display LED is a SMD device that displays the status of all pin counts, making circuit defects easy to find out.

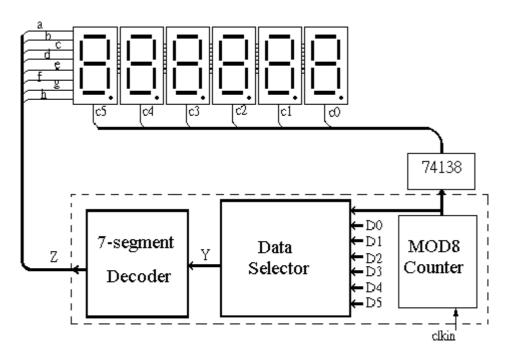

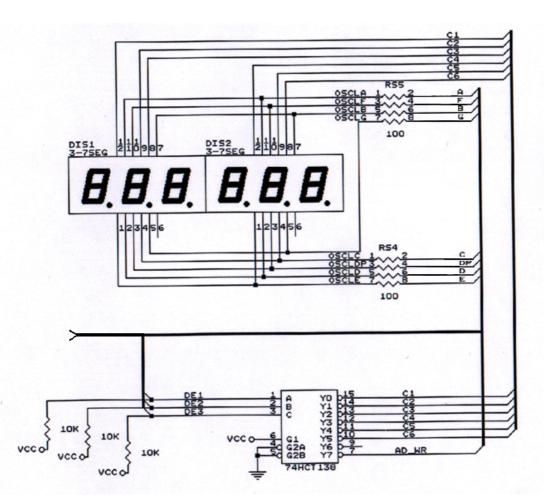

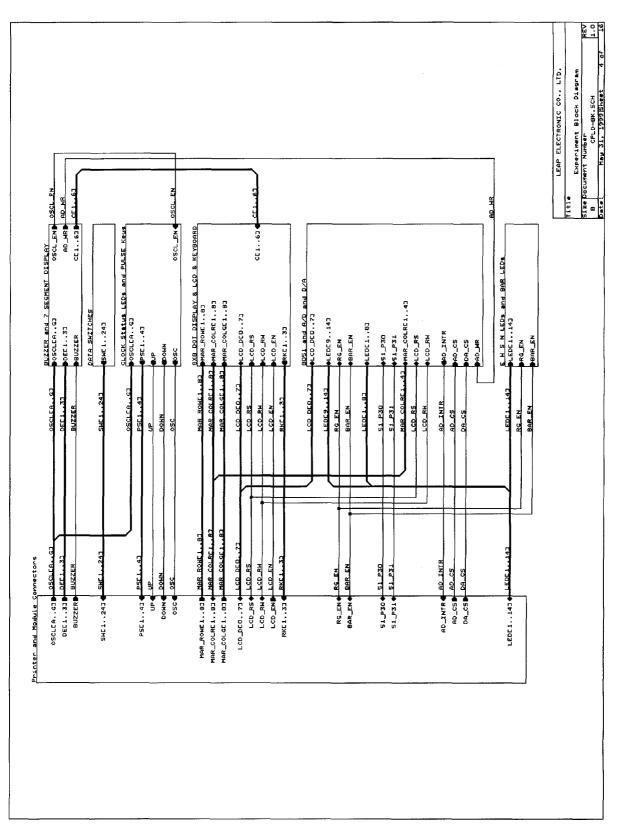

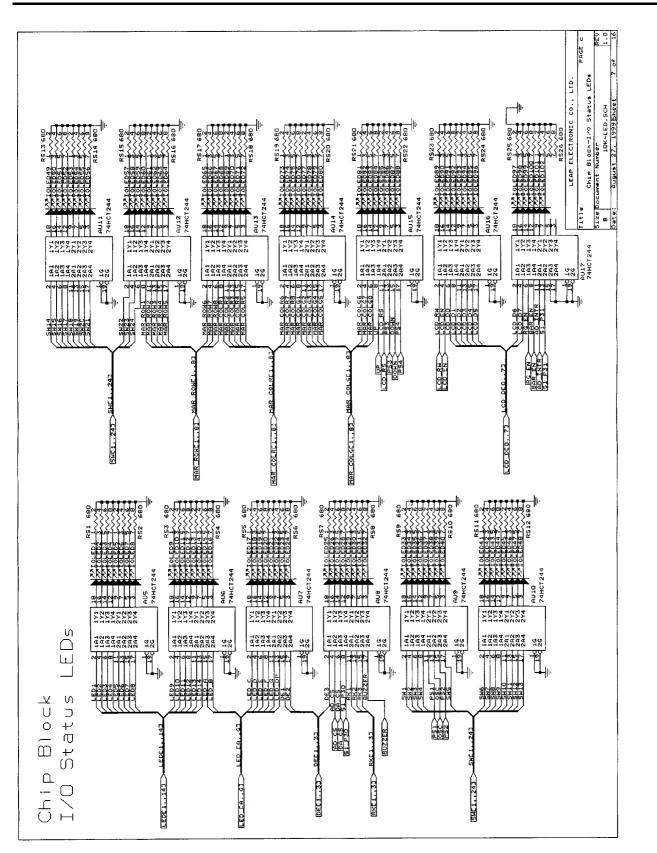

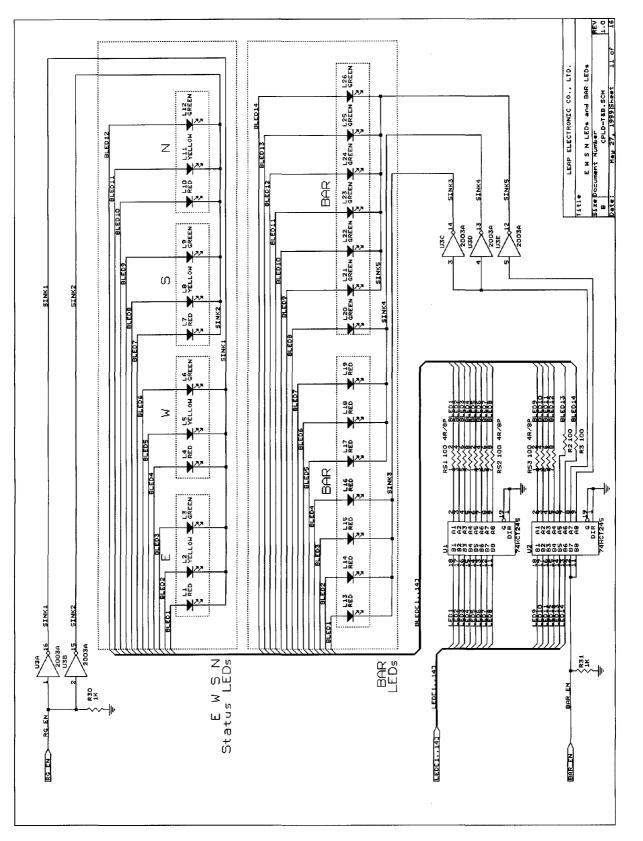

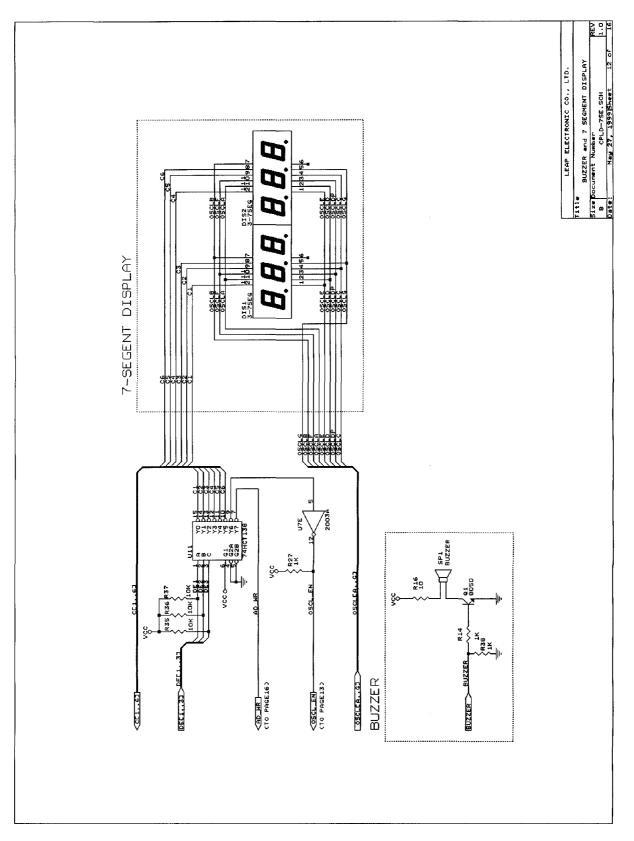

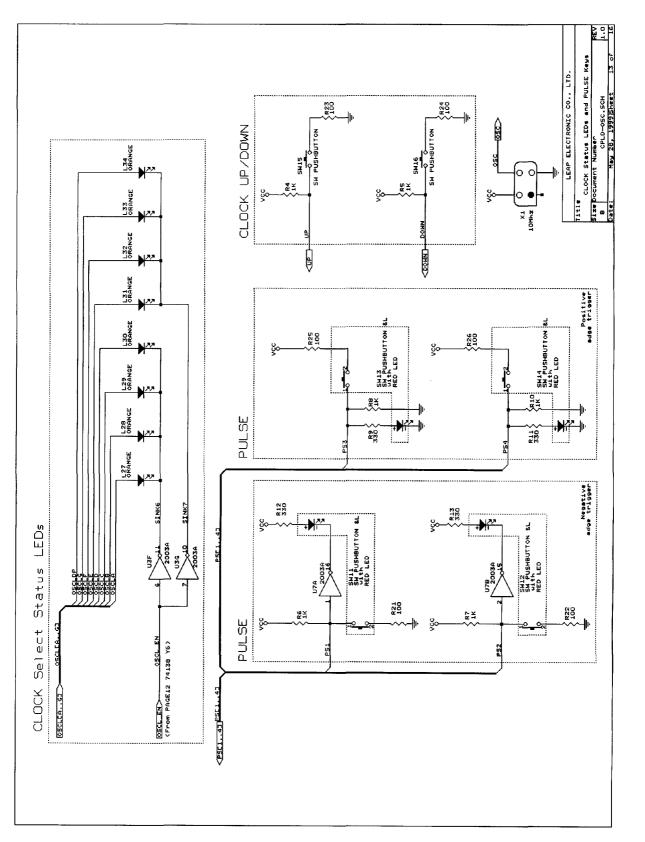

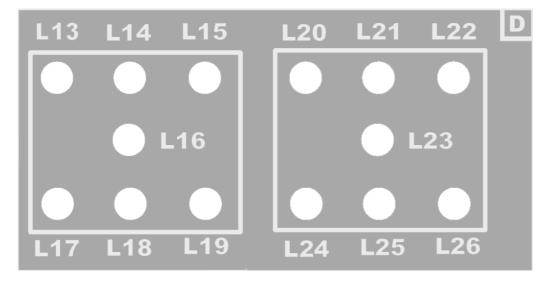

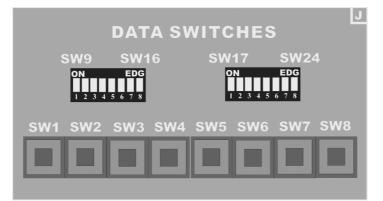

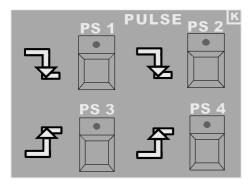

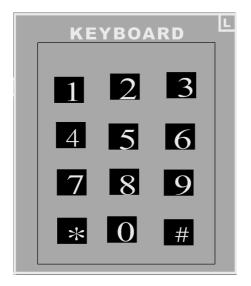

#### ✤ I/O element experimental board

The big board under CPLD devices is I/O element experimental board. This big board totally has 12 different I/O elements including: 1.) 4 sets of red, yellow, and green LED; 2.) 6 common cathode 7-segment displays; 3.) One buzzer; 4.) Two electronic dices; 5.) One clock circuit; 6.) 3 sets of 8-bit data switches; 7.) 4 pulse switches; 8.) One 4×3 keyboard; 9.) One 8×8 dot matrix display; 10.) One LCD display; 11.) A/D & D/A circuit modules, and 12.) 8051 module. The experimental board almost includes all I/O elements generally used in digital logic circuits. It provides a whole completed learning environment or fast prototyping circuit design environment.

Figure 1.18 Overview of LP-2900 CPLD logic design experimental platform

#### PC Printer Download Interface

To program 10K devices, a download interface provides a great convenient parallel channel to download "configuration data" from a PC printer port. It is not necessary to install or remove interface, but plug in printer cables.

#### ✤ Power

AC 90V $\sim$ 260V 50/60Hz, 2A input provides power for all circuits and has short

circuit protection.

Other reference, please see Chapter 9 in this book.

## **1.6 Evaluation and Test**

Please answer the following questions to review this chapter.

- Do you know what benefits of digital systems are better than analog systems?

- □ Do you know what characteristics A/D converters and D/A converters play respectively?

- Do you know what design environments are introduced in this chapter?

- □ Could you indicate what types of devices are been used by engineers today?

- Do you know why standard logic devices would be gradually disappeared?

- □ Do you know the factors making "Integrated Digital Logic Design Environment"?

- □ Could you name some of PLD suppliers?

- □ Could you explain why ALTERA 8K and 10K devices are able to continuously download and program new circuits?

# CHAPTER 2

# Numerical System

In the digital world, it is unavoidable to describe something by numbers. How many numerical systems expressing numbers are in the digital world? How do they express? In this chapter, we will focus on conversion and expression of those numerical systems. We also will introduce binary arithmetic and BCD codes in this chapter.

## 2.1 Numeric Expressions

Because humans have ten fingers and toes, naturally we would like to count numbers by our fingers, and that is what we called "decimal system". In another words, each number is from 0 to 9 (unit, decimal, hundred), and then carry to next digits after counting to 10. Decimal system is the most popular numerical system in our lives. Beside decimal, there also have binary, octal, and hexadecimal commonly used in numerical systems. Table 2.1 indicates the common expressions of the numerical systems.

A numerical system's base is the number of the symbols included in this system. Decimal system, for example, has 10 symbols of 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. Therefore its base is 10. Each weight in numerical systems is the multiple of the base of its previous weight. For instance, 2725D is a four-digit number.

| Numerical System | Expression                                       | Example       |

|------------------|--------------------------------------------------|---------------|

| Decimal          | Add D (decimal) after the last digit (omissible) | 1245D or 1245 |

| Binary           | Add B (binary) after the last digit              | 01010101B     |

| Octal            | Add O (octal) after the last digit               | 47670         |

| Hexadecimal      | Add H (hexadecimal) after the last digit         | 1A2FH         |

Table 2.1

Numerical system common expression

Therefore, 2725D is  $2 \times 10^3 + 7 \times 10^2 + 2 \times 10^1 + 5 \times 10^0$ .

In general, an r-base numerical system uses the numbers from 0 to r-1. Value N could be express by an r-base system as below:

$$N = a_n \times r^n + a_{n-1} \times r^{n-1} + a_{n-2} \times r^{n-2} + a_{n-3} \times r^{n-3} + \dots + a_1 \times r^1 + a_0 \times r^0$$

In the equation, "n" represents 0, 1, 2, 3, … The symbol "r" is the base of the numerical system, and "a" is the number from 0 to r - 1.

For value N from 0 to 1 could be expressed:

$$N = a_{-1} \times r^{-1} + a_{-2} \times r^{-2} + a_{-3} \times r^{-3} + a_{-4} \times r^{-4} + \dots + a_{-n+1} \times r^{-n+1} + a_{-n} \times r^{-n}$$

Thus, a decimal fraction 0.8125 is:

$$\begin{aligned} 0.8125 &= 0.8000 + 0.0100 + 0.0020 + 0.0005 \\ &= 8 \times 10^{-1} + 1 \times 10^{-2} + 2 \times 10^{-3} + 5 \times 10^{-4} \\ &= a_{-1} \times 10^{-1} + a_{-2} \times 10^{-2} + a_{-3} \times 10^{-3} + a_{-4} \times 10^{-4} \end{aligned}$$

Where

$$a_{-1} = 8$$

,  $a_{-2} = 1$ ,  $a_{-3} = 2$  and  $a_{-4} = 5$

### 2.1.1 Binary

As mentioned before, a numerical system base is the number of the symbols used in the system. For a binary system, it has 2 symbols: 0 and 1. Therefore its base is 2. In numerical systems, each weight is the multiple of the base of the previous weight; for example, 01001100B:

0its weight is

$$2^0$$

0its weight is  $2^1 = 2^0$  (the weight of 0)  $\times 2$ 1its weight is  $2^2 = 2^1$  (the weight of 0)  $\times 2$ 1its weight is  $2^3 = 2^2$  (the weight of 1)  $\times 2$ 0its weight is  $2^4 = 2^3$  (the weight of 1)  $\times 2$ 0its weight is  $2^5 = 2^4$  (the weight of 0)  $\times 2$ 1its weight is  $2^6 = 2^5$  (the weight of 0)  $\times 2$ 0its weight is  $2^6 = 2^5$  (the weight of 0)  $\times 2$ 0its weight is  $2^7 = 2^6$  (the weight of 1)  $\times 2$

Therefore,  $01001100B = 0 \times 2^7 + 1 \times 2^6 + 0 \times 2^5 + 0 \times 2^4 + 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 0 \times 2^0$ . For value N from 0 to 1, its binary expression is:

$$N = a_{-1} \times 2^{-1} + a_{-2} \times 2^{-2} + a_{-3} \times 2^{-3} + a_{-4} \times 2^{-4} + \dots + a_{-n+1} \times 2^{-n+1} + a_{-n} \times 2^{-n}$$

The binary expression of 0.1101B is:

$$0.1101B = 0.1000 + 0.0100 + 0.0000 + 0.0001$$

$$= 1 \times 2^{-1} + 1 \times 2^{-2} + 0 \times 2^{-3} + 2 \times 2^{-4}$$

#### 2.1.2 Octal

Because a base is the number of symbols used in a numerical system, an octal

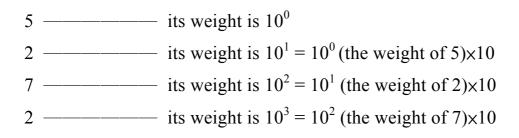

numerical system therefore has 8 symbols including 0, 1, 2, 3, 4, 5, 6, and 7, and its base is 8. In a numerical system, each weight is the multiple of the base of the previous weight. For further understanding, we make an example, 37014O:

Therefore,  $37014O = 3 \times 8^4 + 7 \times 8^3 + 0 \times 8^2 + 1 \times 8^1 + 4 \times 8^0$ For value N from 0 to 1, its octal expression is:

$$N = a_{-1} \times 8^{-1} + a_{-2} \times 8^{-2} + a_{-3} \times 8^{-3} + a_{-4} \times 8^{-4} + \dots + a_{-n+1} \times 8^{-n+1} + a_{-n} \times 8^{-n}$$

Thus, the octal of 0.2154O is:

$$0.2154O = 0.2000 + 0.0100 + 0.0050 + 0.0004$$

$$= 2 \times 8^{-1} + 1 \times 8^{-2} + 5 \times 8^{-3} + 4 \times 8^{-4}$$

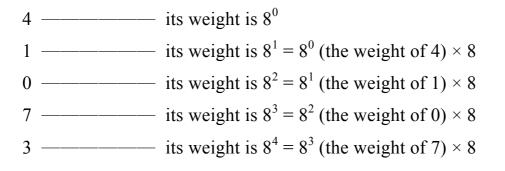

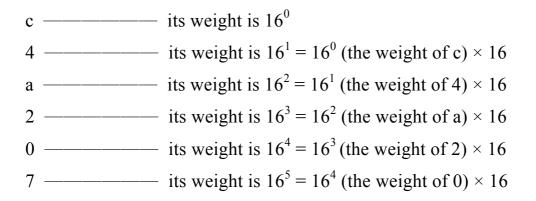

#### 2.1.3 Hexadecimal

A base of a numerical system is the number of symbols used in the system. For a hexadecimal system, its base is 16, having 16 symbols: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. The letters A, B, C, D E, and F represent the values of 10, 11, 12, 13, 14, and 15. Each weight is the multiple of the base of the previous weight. 702a4cH, for example, is a six-digit hexadecimal number.

Thus, 702a4cH is  $7 \times 16^5 + 0 \times 16^4 + 2 \times 16^3 + a \times 16^2 + 4 \times 16^1 + c \times 16^0$ . For value N from 0 to 1, its hexadecimal expression is as below:

$$N = a_{-1} \times 16^{-1} + a_{-2} \times 16^{-2} + a_{-3} \times 16^{-3} + a_{-4} \times 16^{-4} + \dots + a_{-n+1} \times 16^{-n+1} + a_{-n} \times 16^{-n+1} + \dots + a_{-n+1} \times 16^{-n+1} + \dots + a_{-n} \times 16^{-n+1} + \dots + a_{-n+1} \times 16^{-n+1} + \dots$$

The hexadecimal expression of 0.2c09H is:

$$0.2c09H = 0.2000 + 0.0c00 + 0.0000 + 0.0009$$

$$= 2 \times 16^{-1} + c \times 16^{-2} + 0 \times 16^{-3} + 9 \times 16^{-4}$$

## 2.2 Numerical System Conversion

Usually people use decimal systems for daily bases, but computers use binary or hexadecimal systems. It is unavoidable to make a conversion between various numerical systems. Normally we could find binary mutually exchanging with decimal, binary mutually converting with hexadecimal, and hexadecimal mutually converting with decimal.

### 2.2.1 Binary vs. Decimal Conversion

#### Binary-to-Decimal Conversion

It is very easy to convert an r-base number to a decimal number. It only needs to sum up the products of all digits multiplied by weight values. For example:

$$101011.011B = 1 \times 2^{5} + 0 \times 2^{4} + 1 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0} + 0 \times 2^{-1} + 1 \times 2^{-2} + 1 \times 2^{-3}$$

= 1 \times 32 + 1 \times 8 + 1 \times 2 + 1 + 1 \times 0.25 + 1 \times 0.125

= 43.375D

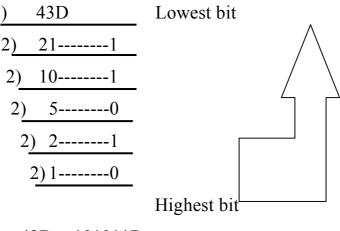

#### Decimal-to-Binary Conversion

In general, a value N that we usually called is a decimal. To make a conversion from decimal to binary, we could use binary expression to find out each "a" factor. The conversion process is shown as below:

$$N = a_{-n} \times 2^{n} + a_{-n-1} \times 2^{n-1} + a_{-n-2} \times 2^{n-2} + a_{-n-3} \times 2^{n-3} + \dots + a_1 \times 2^1 + a_0 \times 2^0$$

=  $(a_{-n} \times 2^{n-1} + a_{-n-1} \times 2^{n-2} + a_{-n-2} \times 2^{n-3} + a_{-n-3} \times 2^{n-4} + \dots + a_1) \times 2 + a_0$

(After N divided by 2, and the remainder is  $a_0$ )

$$= ((a_{-n} \times 2^{n-2} + a_{-n-1} \times 2^{n-3} + a_{-n-2} \times 2^{n-4} + a_{-n-3} \times 2^{n-5} + \dots + a_{-2}) \times 2 + a_1) \times 2 + a_0$$

(After the quotient divided by 2, and the remainder is  $a_{-1}$ )

$= (((a_{-n} \times 2^{n-3} + a_{-n-1} \times 2^{n-4} + a_{-n-2} \times 2^{n-5} + \dots + a_{-3}) \times 2 + a_{-2}) \times 2 + a_1) \times 2 + a_0$ After the new quotient divided by 2, and the remainder is  $a_{-2}$ . We then proceed the same process until the quotient is smaller than 2.

For further explanation, we make an example, 43D converting to binary, as below:

43D = 101011B

## 2.2.2 Octal-to-Decimal Conversion

#### ✤ Octal-to-Decimal Conversion

We already know it is easy to convert an r-base number to a decimal number and it only needs to sum up products of all digits multiplied by weight values. Thus,

$$370.14O = 3 \times 8^{2} + 7 \times 8^{1} + 0 \times 8^{0} + 1 \times 8^{-1} + 4 \times 8^{-2}$$

$$= 3 \times 64 + 7 \times 8 + 1 \times 8^{-1} + 4 \times 8^{-2}$$

$$= 192 + 56 + 0.125 + 0.0625$$

$$= 248.1875D$$

#### Decimal-to-Octal Conversion

In general, a value N that we usually called is a decimal. To make a conversion from decimal to octal, we could use octal expression to find out each "a" factor. The conversion process is shown as below:

$$N = a_{-n} \times 8^{n} + a_{-n-1} \times 8^{n-1} + a_{-n-2} \times 8^{n-2} + a_{-n-3} \times 8^{n-3} + \dots + a_1 \times 8^1 + a_0 \times 8^0$$

=  $(a_{-n} \times 8^{n-1} + a_{-n-1} \times 8^{n-2} + a_{-n-2} \times 8^{n-3} + a_{-n-3} \times 8^{n-4} + \dots + a_1) \times 8 + a_0$

(After N divided by 8, and the remainder is  $a_0$ )

$$= ((a_{-n} \times 8^{n-2} + a_{-n-1} \times 8^{n-3} + a_{-n-2} \times 8^{n-4} + a_{-n-3} \times 8^{n-5} + \dots + a_{-2}) \times 8 + a_1) \times 8 + a_0$$

(After quotient is divided by 8, and the remainder is  $a_1$ )

= ((( $a_{-n} \times 8^{n-3} + a_{-n-1} \times 8^{n-4} + a_{-n-2} \times 8^{n-5} + \dots + a_{-3}) \times 8 + a_{-2}) \times 8 + a_1) \times 8 + a_0$

The remainder of the new quotient divided by 8 is  $a_{-2}$ ; follow the same process until quotient is smaller than 8.

For example, 243D converting to an octal number is as below:

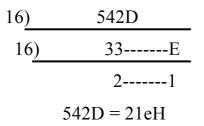

8) 243D

8) 30-----3

$$3$$

-----6

243D = 363O

### 2.2.3 Hexadecimal-to-Decimal Conversion

Hexadecimal-to-Decimal Conversion

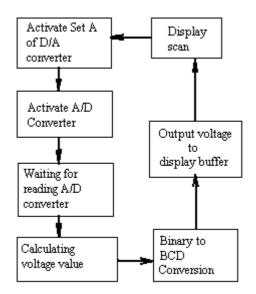

We already know it is easy to convert an r-base number to a decimal number and it only needs to sum up products of all digits multiplied by weight values. Thus,